Other Parts Discussed in Thread: ADC12DJ3200, LMK04828

Hi team

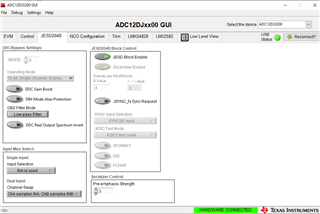

I am using ADC12DJ3200 operated in JMODE 0 with Fs=1250 MSPS. The Serdes is operated at 5 Gbps. FPGA Clock generated from LMK04828 is 125 Mhz (with DCLK=10). i am using ADC internal test mode patterns for my testing. Below is the screenshot of the JESD204B setting in the ADC GUI:

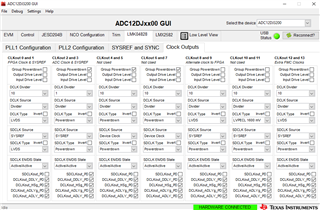

LMK04828 clock outputs are set as :

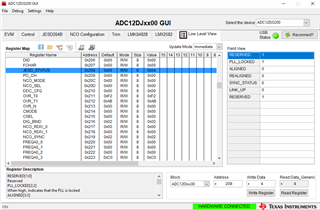

But when i program my adc device with this settings, my JESD link status is not getting up. Also sync signal is always low as shown below

Am i missing anything here? Looking forward to your reply.

Regards

Rohit