Other Parts Discussed in Thread: ADS4225

Hi

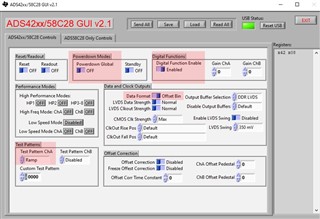

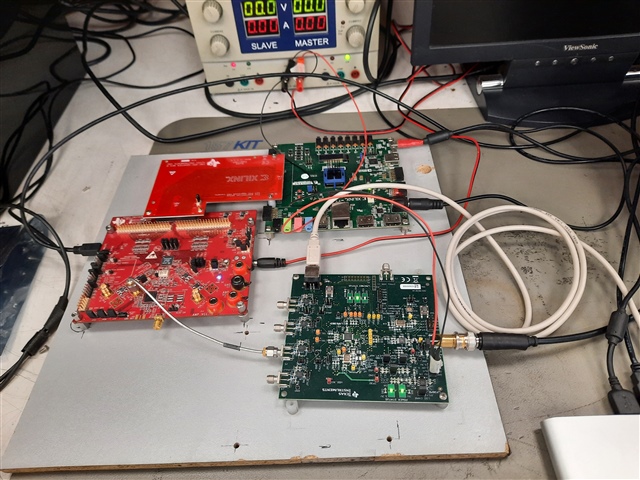

I have some issues getting signal from ADS4225EVM. This is the setup:

The stup consists:

- SD1983EVK

- ADC-FMC adapter

- ADS4225EVM

- Nexys Video (Based on Xc7-A200T)

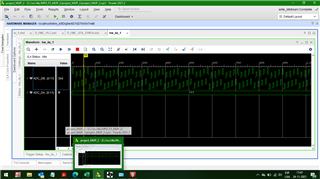

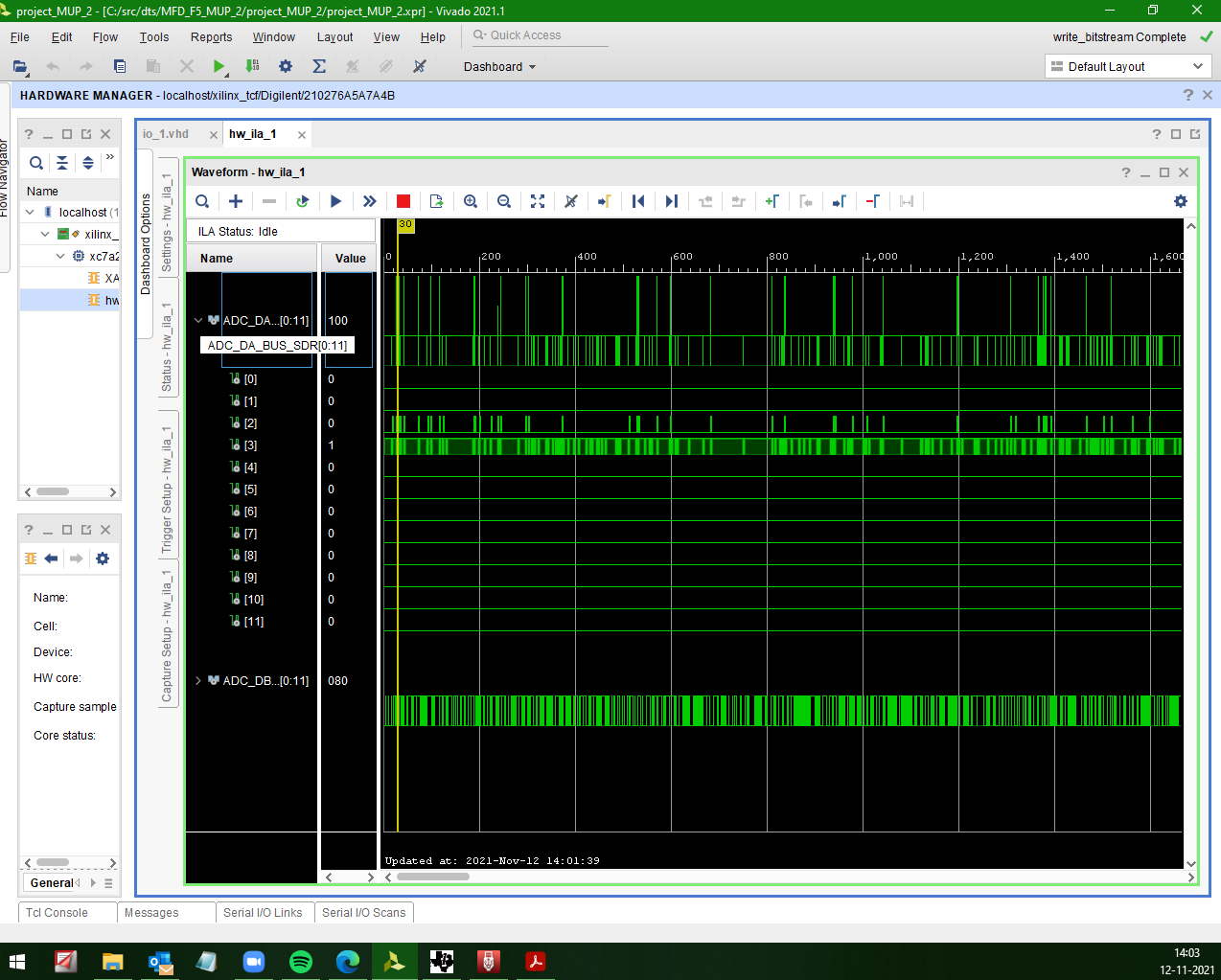

I'm getting just the third and fourth bits, but no others. I don't know why is this happening . Board has default settings and using the software I put on the ramp pattern generator. Instead of a ramp, I'm getting this:

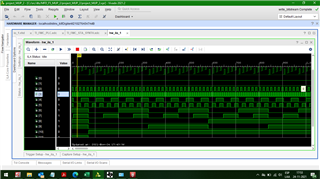

I made a simulation and I expected to see something like this:

I also ensured that the FMC voltage selector in the fpga side is set properly (1.8v), and mapping is apparently ok. Here's a table:

| ADC-FMC | Nexys Video | ||||

| ADC ADS42XX | J2 | J1 | FPGA | ||

| IO_0P | N/C | G9 | FMC_LA_03_P | ||

| IO_0N | N/C | G10 | FMC_LA_03_N | ||

| IO_1P | DB12 | G12 | FMC_LA_08_P | ||

| IO_1N | DB12 | G13 | FMC_LA_08_N | ||

| IO_2P | DB10 | H13 | FMC_LA_07_P | ||

| IO_2N | DB10 | H14 | FMC_LA_07_N | ||

| IO_3P | DB8 | G15 | FMC_LA_12_P | ||

| IO_3N | DB8 | G16 | FMC_LA_12_N | ||

| IO_4P | DB6 | H16 | FMC_LA_11_P | ||

| IO_4N | DB6 | H17 | FMC_LA_11_N | ||

| IO_5P | DB4 | G18 | FMC_LA_16_P | ||

| IO_5N | DB4 | G19 | FMC_LA_16_N | ||

| IO_6P | DB2 | H19 | FMC_LA_15_P | ||

| IO_6N | DB1 | H20 | FMC_LA_15_N | ||

| IO_7P | DB0 | H22 | FMC_LA_19_P | ||

| IO_7N | DB0 | H23 | FMC_LA_19_N | ||

| IO_8P | DA12 | G21 | FMC_LA_20_P | ||

| IO_8N | DA12 | G22 | FMC_LA_20_N | ||

| IO_9P | DA10 | G24 | FMC_LA_22_P | ||

| IO_9N | DA10 | G25 | FMC_LA_22_N | ||

| IO_10P | DA8 | H25 | FMC_LA_21_P | ||

| IO_10N | DA8 | H26 | FMC_LA_21_N | ||

| IO_11P | DA6 | H28 | FMC_LA_24_P | ||

| IO_11N | DA6 | H29 | FMC_LA_24_N | ||

| IO_12P | DA4 | G27 | FMC_LA_25_P | ||

| IO_12N | DA4 | G28 | FMC_LA_25_N | ||

| IO_13P | DA2 | C18 | FMC_LA_14_P | ||

| IO_13N | DA2 | C19 | FMC_LA_14_N | ||

| IO_14P | DA0 | H31 | FMC_LA_27_P | ||

| IO_14N | DA0 | H32 | FMC_LA_27_N | ||

| IO_15P | D26 | FMC_LA_28_P | |||

| IO_15N | D27 | FMC_LA_28_N | |||

| IO_16P | G33 | FMC_LA_31_P | |||

| IO_16N | G34 | FMC_LA_31_N | |||

| IO_17P | G36 | FMC_LA_33_P | |||

| IO_17N | G37 | FMC_LA_33_N | |||

| IO_18P | H7 | FMC_LA_02_P | |||

| IO_18N | H8 | FMC_LA_02_P | |||

| IO_19P | H10 | FMC_LA_04_P | |||

| IO_19N | H11 | FMC_LA_04_N | |||

| IO_20P | C10 | FMC_LA_06_P | |||

| IO_20N | C11 | FMC_LA_06_N | |||

| IO_21P | D11 | FMC_LA_05_P | |||

| IO_21N | D12 | FMC_LA_05_N | |||

| IO_22P | C14 | FMC_LA_10_P | |||

| IO_22N | C15 | FMC_LA_10_N | |||

| IO_23P | D23 | FMC_LA_23_P | |||

| IO_23N | D24 | FMC_LA_23_N | |||

| IO_24P | C26 | FMC_LA_27_P | |||

| IO_24N | C27 | FMC_LA_27_N | |||

| IO_25P | G30 | FMC_LA_29_P | |||

| IO_25N | G31 | FMC_LA_29_N | |||

| IO_26P | H34 | FMC_LA_30_P | |||

| IO_26N | H35 | FMC_LA_30_N | |||

| IO_27P | H37 | FMC_LA_32_P | |||

| IO_27N | H38 | FMC_LA_32_N | |||

| FCLKP | G6 | FMC_LA_00_P | K18 | ||

| FCLKN | G7 | FMC_LA_00_N | K19 | ||

| DCLKP | D20 | FMC_LA_17_P | |||

| DCLKN | D21 | FMC_LA_17_N | |||

| SDATA | D17 | FMC_LA_13_P | |||

| SCLK | D18 | FMC_LA_13_N | |||

| SPI_1 | D14 | FMC_LA_09_P | |||

| SEN | D15 | FMC_LA_09_N |

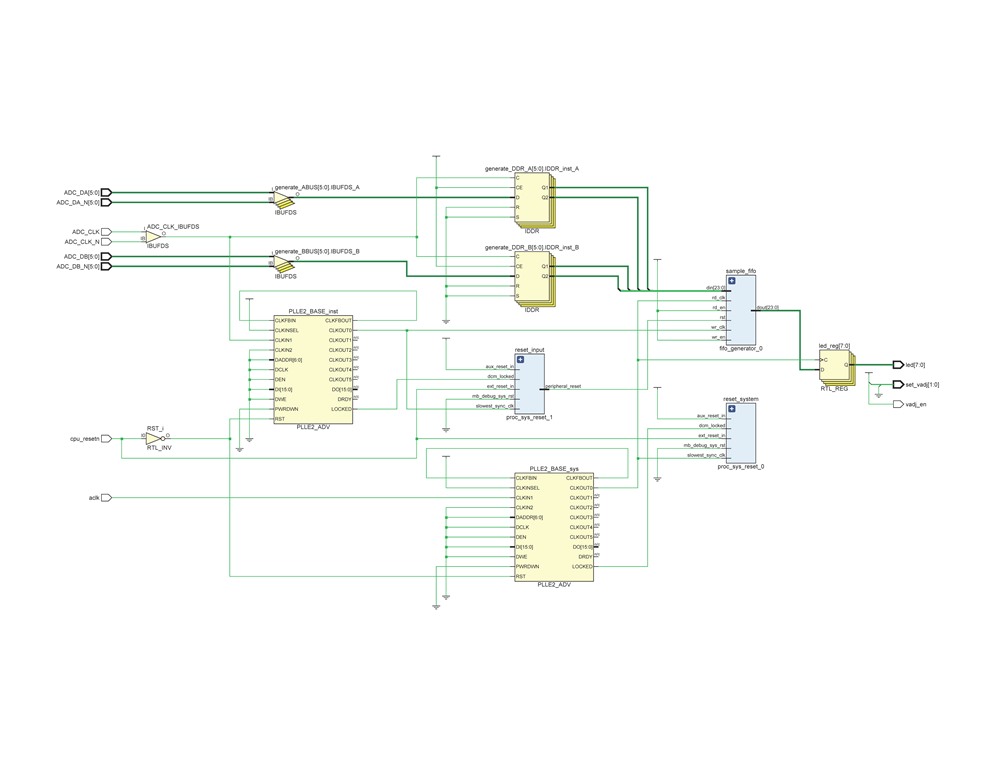

Here's the rtl diagram that i'm using to digitize this:

Any advice to get proper signal is welcome

Thanks