Hi

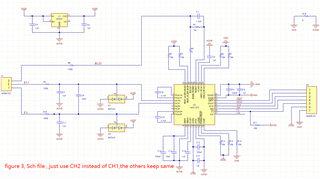

I'm using ADS1292R to obtain EMG signal, I use only one channel--ch2 and I set Ch1 to power down mode. during my dubug process, I found something that I can't understand,the following is my issues:

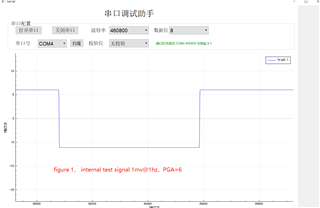

1: I'm sure my control code for SPI bus works well, if I set chip internal test signal 1mV@1Hz, I can see the correct rusult.

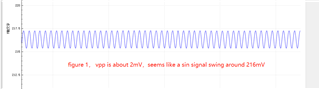

2: If I set MUX1[3:0] of CH2SEL regesiter to 000( Normal electrode input) ,the adc results is shown as following figure 1(Y axis uint: mV,X axis unit : Sec):

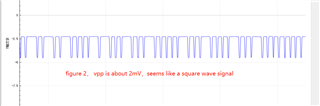

3:If I make input pins CH2P and CH2N shorted, the adc result is shown as following figure 2(Y axis uint : mV,X axis unit : Sec):

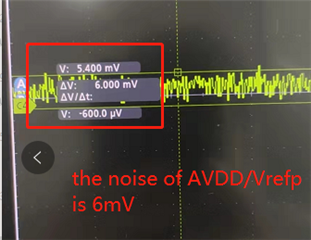

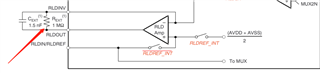

4: Vcap1 =1.2V, Vcap2 =4.99V, AVDD = 3.0V, DVDD=3.3V, and the voltage of RLDOUT is 2.92V(this voltage doesn't looks normal )

5: My sch file is shown as figure 3,

6: If I shorted CH2P and CH2N ,or make CH2 in normal mode, the output result of system should be a straight base line with a little fluctuation under the idle state。

Under this situation, I can never get EMG signal, the noise signal is too large for EMG signal,

Any help will be highly appreciated as I have limited time. Thank you