Hello E2E,

I understand that the DRDY pin will switch to Low when the ADC completes the data conversion.

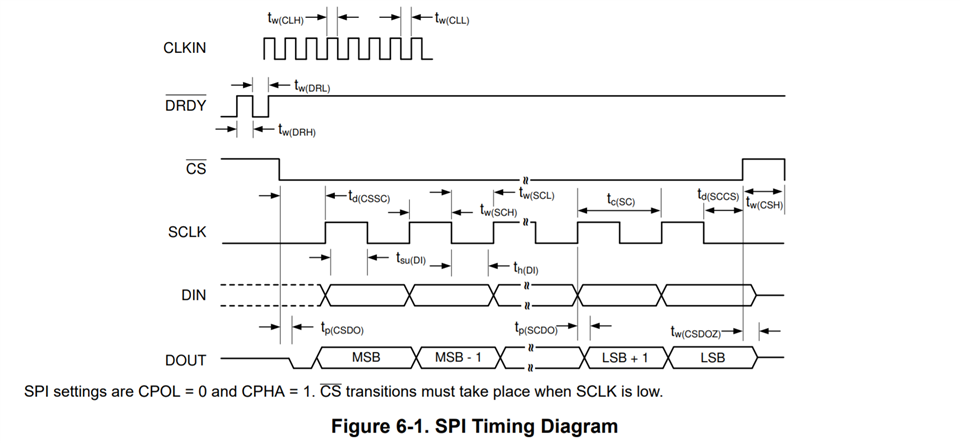

Normally, DRDY is input to the interrupt trigger of the MCU and then SPI communication is performed with the ADC, but in our usage, there is another priority process, the timing to start SPI communication is delayed, and the next DRDY SPI communication may not end even at the timing.

I'm currently looking at OSR128 and 64 (TBM bit 1) and OSR256.

When the above conflict occurs, the phenomenon that DRDY goes low is usually seen in half the time when DRDY goes low.

For example, if the DRDY is set to be Low in a 128us cycle, it will be wavy if the interval at which the DRDY is Low is constant as 128us-> 64us-> 128us-> 128us.

What time is the latch timing of the ADC data at this time?

Regards,

ACGUY