Other Parts Discussed in Thread: ADS8900B,

Hello

I have to design an analog to digital convertion stage with a high accuracy (RMS value error < 0.1%) on a large dynamic of 44dB (62.5mA to 10A).

The number of bits necessary to code the full dynamic is log2(10A/62.5mA) = 7.32 bits.

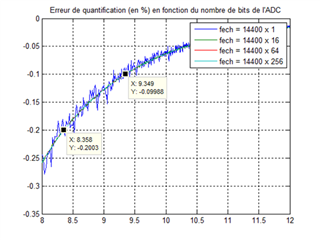

The signal to be mesured being a sine at 50Hz, I have digitalized a normalized 50Hz sinus at a quantification of 2^8 to 2^12 and calculated the RMS value error due to the quantfication :

With this, I have determined that the number of bits necessary to respect the accuracy must be > 9.35 bits.

If no considering the noise, the number of bits of the ADC necessary must be 7.32 + 9.35 = 16.67 bits or the SNR must be greater then 16.67 x 6.02 + 1.76 = 102dB.

In your opinion, is this method seems to be correct?