Hi team,

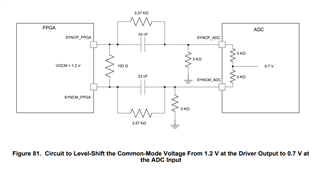

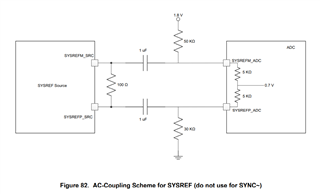

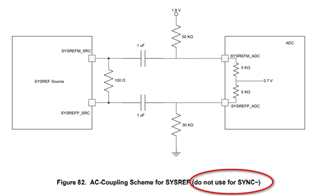

When connecting SYSREF and SYNC, level matching needs to be considered. I see the following connection method in the following FAQ, that is, both SYSREF and SYNC use AC coupling. However, in ADS52J90 datasheet, figure 82 indicates AC coupling scheme for sysref (do not use for sync ~)

[FAQ] ADS52J90: How to terminate SYNC_SERDES, SYSREF_SERDES signals in ADS52J90?:https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/711635/faq-ads52j90-how-to-terminate-sync_serdes-sysref_serdes-signals-in-ads52j90?tisearch=e2e-sitesearch&keymatch=ADS52J90

The FAQ conflicts with the description in the ADS52J90 datasheet. I would like to know which one is correct.

Best Regards,

Amy Luo