Other Parts Discussed in Thread: DAC7750

Hi,

we built a board with two DAC8760 connected in DaisyChain to a Kinetis K22 SPI. Both chips have their own ChipSelect signal.

When adressing the first DAC8760 in the DaisyChain everthing seems to work fine.

Trying to access the second device gives unexpected behaviour in both devices.

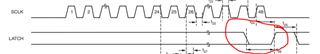

It kinda seems that the first DAC8760 is interpreting some of the data after 24 clock cycles although there is no rising edge of the corresponding ChipSelect signal. Same problem without a solution: https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/471368/dac7750---is-it-possible-for-the-device-to-take-action-on-its-input-shift-register-contents-without-seeing-a-rising-edge-on-latch-if-a-particular-pattern-is-present-on-din-and-sclk

The datasheet is not very accurat on this topic and several forum posts in the E2E forum show an unexpected and not SPI standard behaviour. Unfortunately there is no clear solution or answer on how the latching in daisy chain mode works.

Questions:

- can the ChipSelect signal be low during all transmission with a rising edge at the last bit latching the data? or will the chip latch the data in after 24 bits anyways? the datasheet kinda assumes a dontcare for the 0-23 bits.

- the DAC7750/DAC8760 sample code shows a manual toggle (high-low-high) of the latch pin after transmission of all bits from high to low to high. is this the only way to latch data input? this is the opposite of the dontcare in the datasheet.

- when transmitting 48 bits in DaisyChain (DCEN = 1) the first device seems to latch in data when ChipSelect is low and has no rising edge. this can be read from many forum posts as well. is this normal behaviour?