Hello guys,

One of my customers is evaluating DAC8760 for their new products.

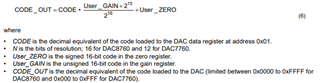

They tried to calibrate DAC8760 VOUT by DAC gain calibration and zero calibration register as the follows.

They could calibrate 10V and 5V output but couldn't calibrate 0V output.

Do you know any way to calibrate 0V output voltage?

[Before user calibration]

DAC gain calibration register = 0x8000

DAC zero calibration register = 0x0000

0V output =0.0049V

5V output =5.0051V

10V output =10.0046V

[After user calibration]

DAC gain calibration register = 0x8003

DAC zero calibration register = 0xFFE2

0V output =0.0047V

5V output =5.0002V

10V output =9.9998V

[DAC8760 power supply]

AVDD=+24V

DVDD=+3.3V

GND=0V

AVSS=-3.3V

Thermal Pad=-3.3V

Could you please give me your reply?

Best regards,

Kazuya.