Hi Team,

The datasheet has changed from Revision C to D.

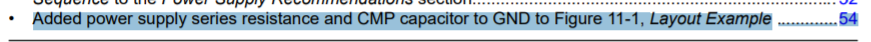

I understand that there are two changes to the recommended circuit:

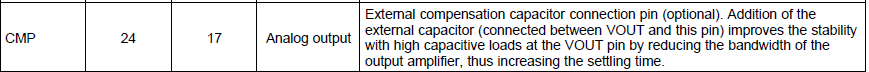

-Additional 100-pF capacitor from CMP to GND

-Additional 10ohm series resistor from the analog supply to the device AVDD

If there is other change(additional) point, could you please let us know this point?

Currently, our circuit don’t have 100pF and 10ohm.

Could you please let us know your concern?

Regards,

Hide