Hi.

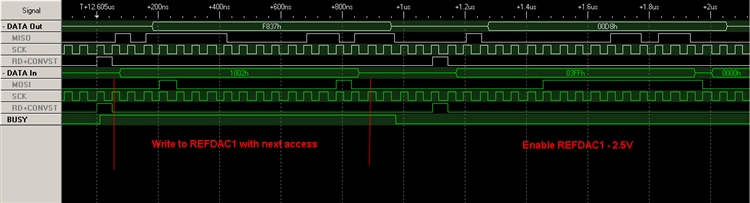

I come from Beijing and have an ADS8363EVM board. There are some problems about the busy time series. I configured the board as follows.

FCK=1MHZ;

VD was 5V;

VA was 5V;

RD connected CONVST;

CMA connected REF1; CMB connected REF2;

M0 was high; M1 was high; SDOB was high impedance;

The SDI data did not write to ADS8363EVM;

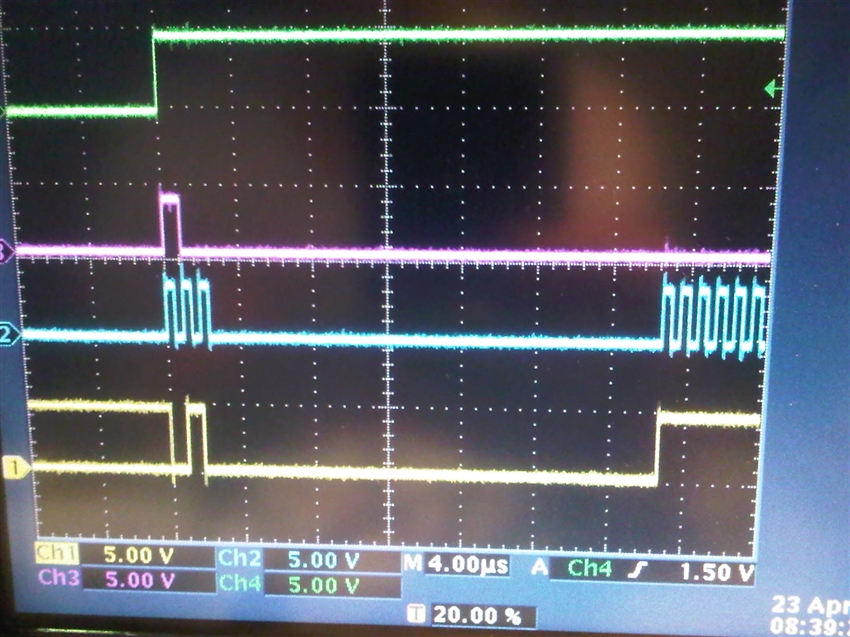

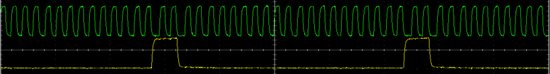

1\ SCK and CONVST time series(SCK was green line and CONVST was yellow line):

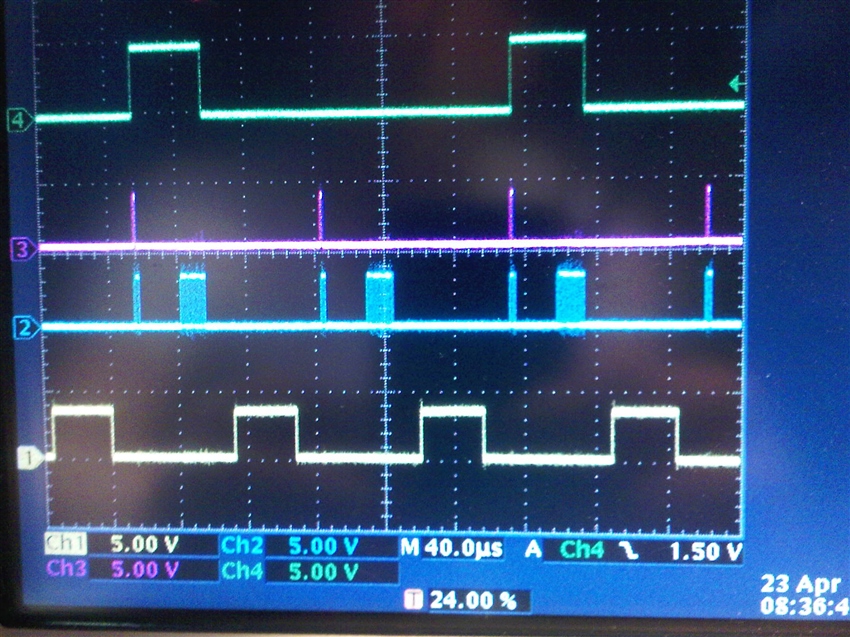

2\ RD and BUSY time series(RD was green line and BUSY was yellow line):

Could you explain what happened to the busy line?

Thank you very much!

Daisy