Other Parts Discussed in Thread: , AFE5808

Hi Team,

Our customer is using AFE5808A and having below questions, can you help to answer them?

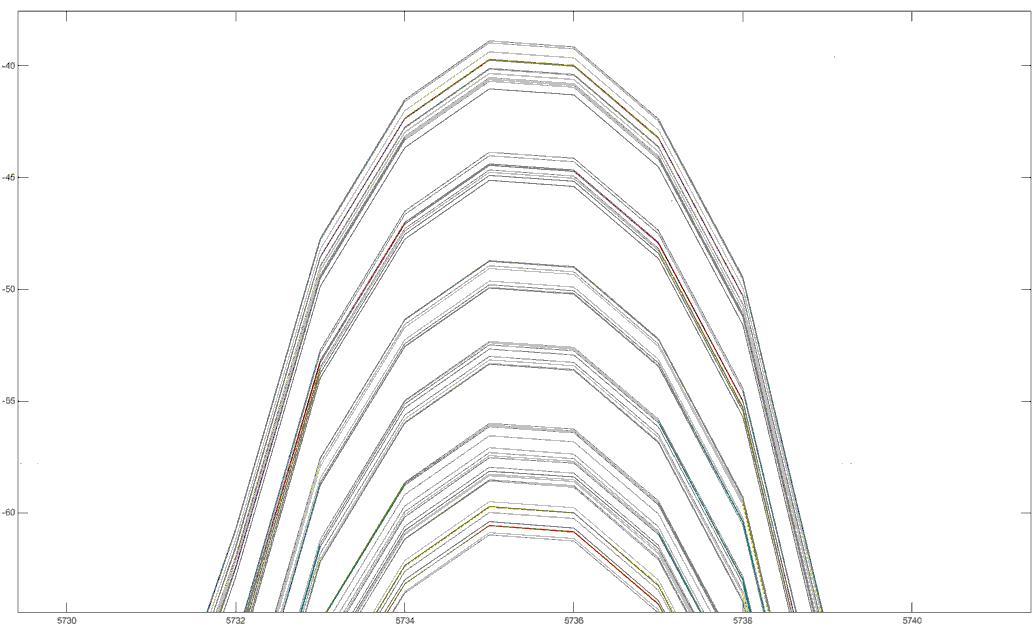

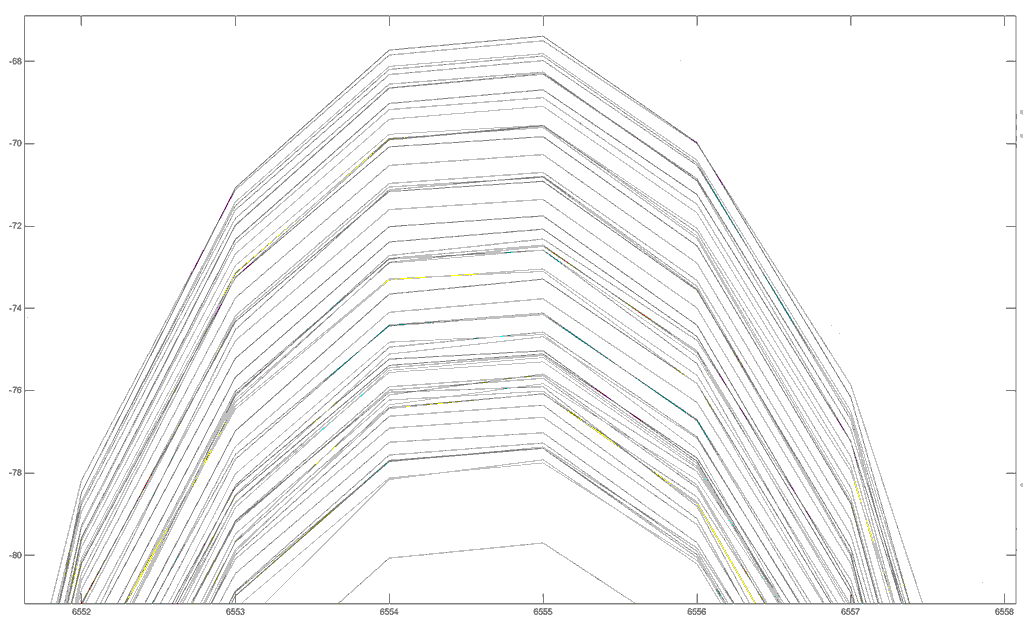

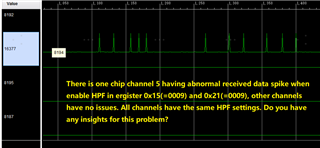

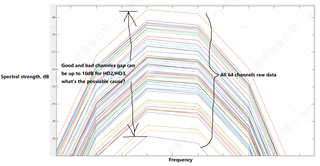

1. When using the same one signal input to multiple AFE channels, but we will see the difference on each channel's 2nd harmonic performance, sometimes it will have 8~20dB gap. Do you know what's the reason for this behavior?

2. Do we have any optimizing suggestion regarding to AFE's receiver saturation recovery performance?

3. Customer is considering to add inductor to discharge low frequency saturation signals on AFE receiver port, but as there is DC bias on AFE receiver port, it may need to pull up inductor to voltage source, do we have any ideas about this problem?

Thanks.