I have some questions about this device, for which I have to write some software.

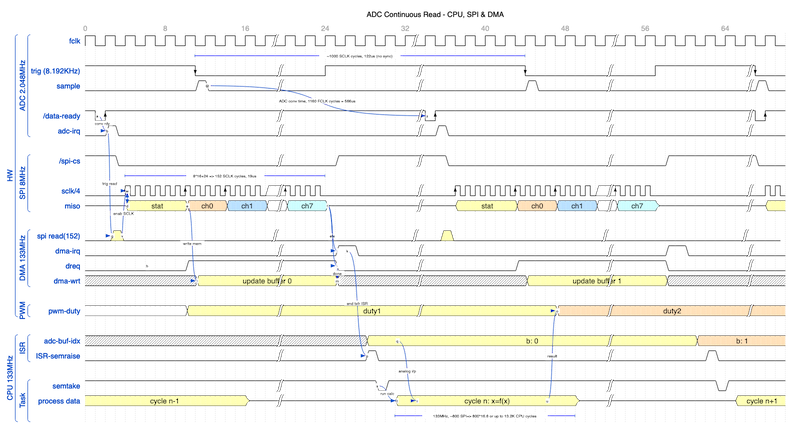

The most pressing is: I would like to use READC mode from a RaspberryPi RP2040 MCU (2x Cortex M0+) using DMA. I'm a bit new to directly using SPI as well.

Given that the SPI master unit uses max 16 bit values, how should I indicate a need for a read of the 24-bit status value? Is it sufficient to program 152 bits worth of data and munge it later? (I really wish it was only a 16 bit status!)

The SPI unit on the RP2040 is the ARM standard library part, PL021 SSP, and has a mode switch for Nat Semi MicroWire or Motorola SPI or TI synchronous serial. I presume I should be using SPI despite this being a TI made device?

I am also at a loss as to how to "ask" the ADC to send SCLK pulses for the read data at the correct time... the only thing I can think of is monitoring the DRDY signal from the ADC to trigger the DMA unit to request a fixed 152 bit frame from the ADC's SPI channel, which would in turn cause SCLK pulses to be sent which the ADC uses to transmit data.... is that right? I'm asking because basically none of the software I have seen code for actually implements READC mode, although some mention it.