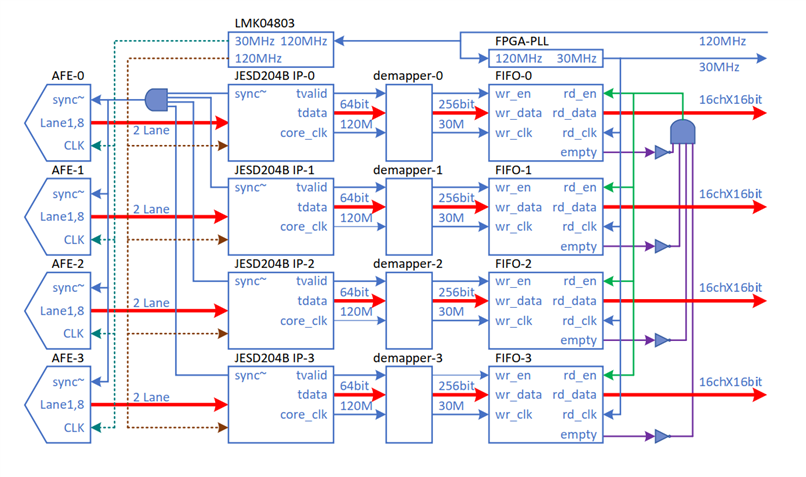

Now I am using FPGA(XCKU3P) to receive sampling data from AFE58JD48 through JESD204B.

The AFE configuration is JESD 160X Mode, Subclass2, 16bit-30MHz sampling rate.

1. How can I sample four AFE synchronously in Subclass2 mode (one board contains one FPGA and four AFE)?

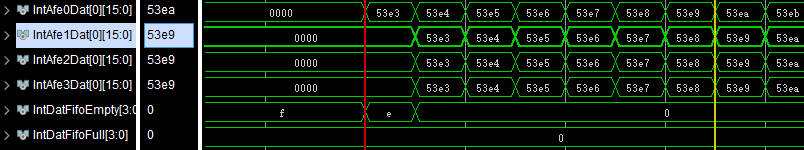

On a single board:First, I set all FIFO read enable to 1, but after device reset, different JESD will be out of sync, as shown in the picture (All channels of an AFE are the same, but the data of different AFE will be out of sync. Only the data of channel 0 of each AFE will be shown here):

At present, I invert the "empty" signal of each FIFO, then to AND these signals together, then distribute this aggregated signal to each fifo as the common read enable signal, as shown in the figure. The problem was solved in this way, but I don't know whether this solution is correct or not.

2. How can I do all AFE synchronous sampling of two boards in Subclass2 mode?

Through the above method, the synchronization problem of single board can be solved, but how to solve the synchronization problem between boards?