The sampling rate i am getting is only half than expected.

According to page 23 of the datasheet at power mode HR with a clockin frequency of 8.192MHZ and a OSR setting of 1024 i should be getting 4 000 sample per second. Instead i am getting only 2000 Samples per second.

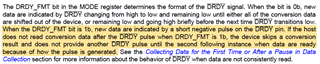

I have not changed any other register settings exempt for the Mode Register setting it to 0x0111 (clearing the RESET bit and setting the DRDY_FMT to pulse mode)

writeSingleRegister(MODE_ADDRESS, 0x0111)

Increasing or decreasing the OSR also yields only half the expected sampling rate. For example

512 - 4ksp/s only instead of 8ksp/s

256 - 8ksp/s only instead of 16ksp/s

128 - 16 ksp/s only instead of 32ksp/s

I think i have narrowed down the culprit. Powering off the device, and turning it back on with ONLY the 8.192Mhz signal (no SPI comunnication was done with the device). I am able to get the 4ksp/s.

But upon executing writeSingleRegister(MODE_ADDRESS, 0x0111). I am getting half of the expected sampling rate

suspecting that my writeSingleRegister function broke some other register settings , i went ahead and read all global-setting registers ( registers 0x02 to 0x08) to check if I indeed corrupted something. Here are the results

| REG ADDRESS | REG NAME | RESET VALUE | MY VALUE |

| 0x02 | MODE | 0x0510 | 0x0111 |

| 0x03 | CLOCK | 0xFFE0 | 0xFFE0 |

| 0x04 | GAIN1 | 0x0000 | 0x0000 |

| 0x05 | GAIN2 | 0x0000 | 0x0000 |

| 0x06 | CFG | 0x0600 | 0x0600 |

| 0x07 | THRSHLD_MSB | 0x0000 | 0x0000 |

| 0x08 | THRSHLD_LSB | 0x0000 | 0x0000 |

I have even tried not touching the MODE_RESET bit by using writeSingleRegister(MODE_ADDRESS, MODE_DEFAULT | 0x0001). It would seem that changing DRDY_FMT causes the problem.

What do i do to get it back to the proper sampling rate while still having a pulse drdy format??