and have a problem on debuging jesd204 interface.

Hi There,

Customer is working on jesd204 interface debugging.

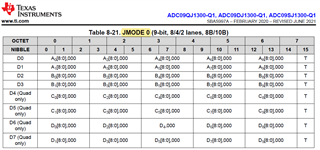

Test condition: adc09qj1300-q1 which is the data transmit end. And also data receive end is FPGA, xilinx's ZYNQ series chip that is 7z100 chip. Data tx send adc samples to rx via jesd204b. ADC's configuration parameter: JMODE = 0(F = 8), K = 4, lane num =8, Fs = 1GSPS. 7z100 's K and F is the same with adc chip, and Serdes speed is 6.25Gbps. Now, at 7z100, i saw jesd204b links up and can get adc tx parameter via AXI4-lite interface.

question: In FPGA, customer wants to de-map the received data whose format is: rx_tvalid、rx_tdata[255:0]、rx_start_of_frame[3:0], rx_end_of_frame[3:0]、rx_start_of_multiframe[3:0]、rx_start_of_multiframe[3:0]. 7z100's user clock is rx_core_clk, and one clock corresponding to 256 bits(rx_tdata[255:0]).

how can we map the different lane's data to rx_tdata[255:0]! even with the explanation on page 79, Table 8-21 of theADC09QJ1300-Q1 datasheet, we still don't know how to do the mapping.

BRs,

Shubiao