Other Parts Discussed in Thread: ADS52J90EVM, , ADS52J90

Hi,

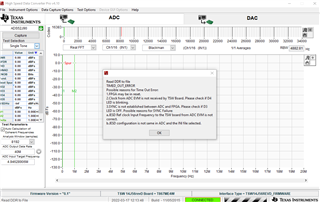

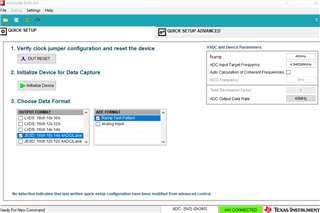

We are testing ADS52J90EVM and we used TSW1265EVM to capture the output data.

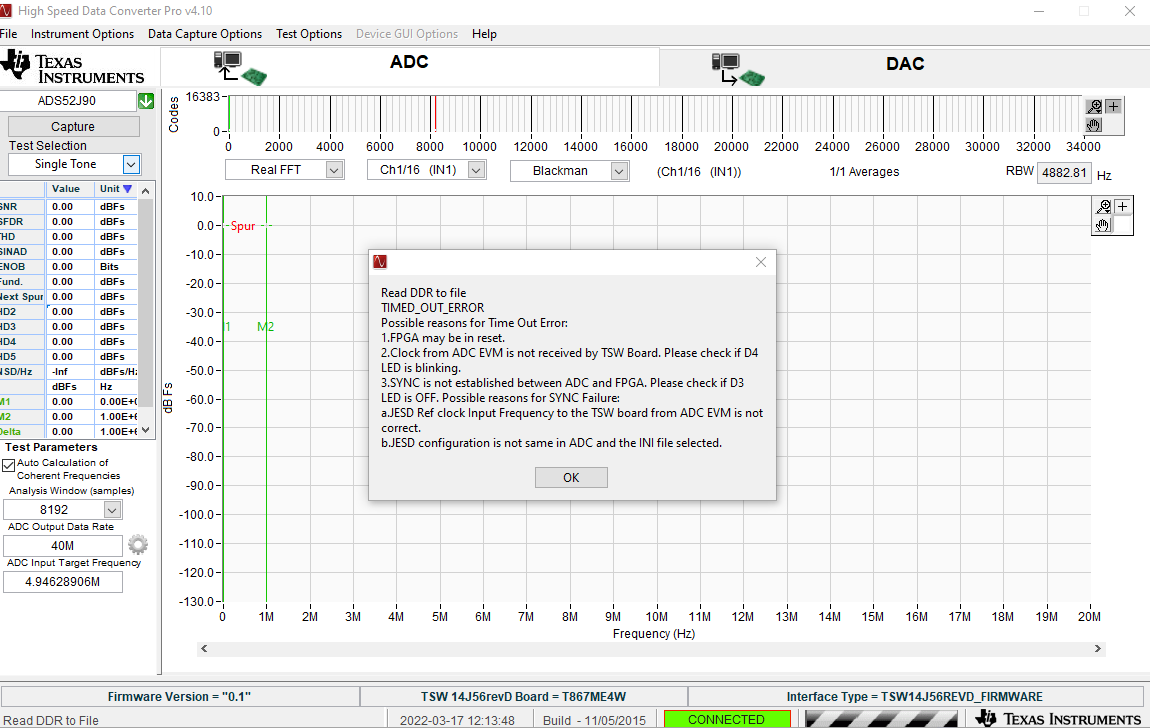

but every time we try we get an error:

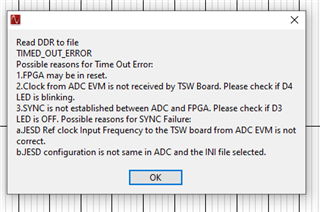

Read DDR to file

TIME_OUT_ERROR

I have checked D4 is not blinking (OFF)

D3 is not OFF (ON)

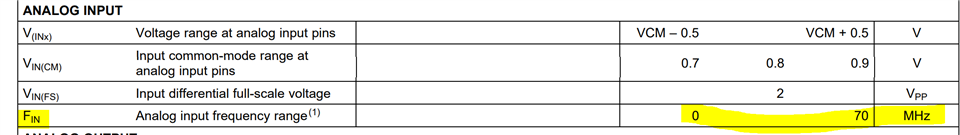

and the input CLK ADS52J90EVM ,J75(LMK _CLKIN1 )is 40/60MHz.

Could you please check this issue?

Best Regards,

Bhaaeddin