Other Parts Discussed in Thread: ADC128S102

Hello,

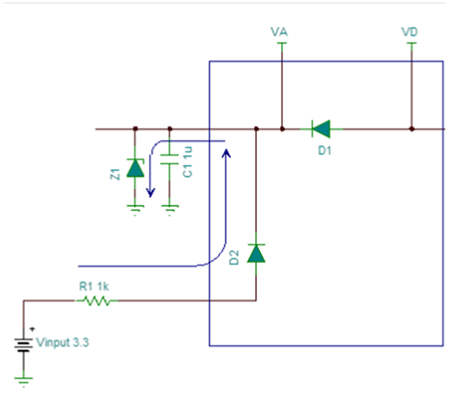

We have an application where the analog inputs are active before the power up of the analog supply (Va) is complete. What are the implications of this condition and how can we improve reliability of the application?