Other Parts Discussed in Thread: LMK04828

Hi team,

Here is a question from one customer.

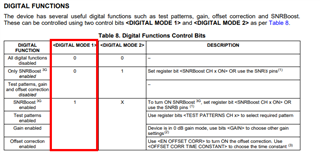

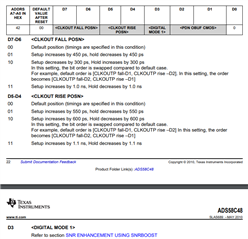

At present, it can communicate with ADS58C48 normally. The FPGA side is configured as DDR LVDS mode.

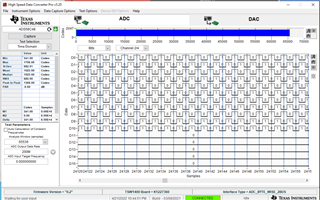

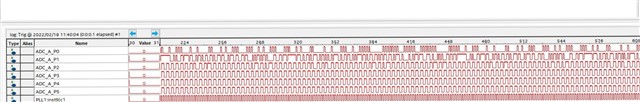

Set the ADC four channel output mode to outputs toggle pattern That is, the output is 10101010101 and 01010101010

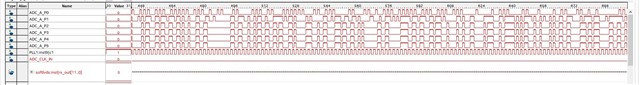

From the FPGA end, it can be seen that on A10, A8, A6 and A4, the data waveform conforms to the set output mode. However, this is not the data mode on the two LVDS lines A2 and A0. The same phenomenon exists in all four channels. Read the ADC register value after configuration, and the configuration value is consistent with the read value.

See the figure for details.

Other tests:

1. Configure output all zeros:

Configure Output all ones:

PLL1 in the figure is the input clock of ADC.

2. The input clock of ADC is the signal directly output by FPGA PLL frequency doubling. The frequency has tried 20M, 40M, 50M, 80M and 100M, and the amplitude is VPP = 2.5V. The clock output is correct, which has been measured and verified by oscilloscope.

3. The CM voltage is 0.95V.

4. This ADC peripheral design can work normally in other projects (the difference from this project is that the FPGA is replaced, but the pin definition and configuration are verified to be OK). The supply voltage, power consumption and configuration resistance of ADC have been measured and there is no problem.

5. The phenomenon is consistent after the PCB is rearranged.

What are the possible reasons for the above phenomenon? Could you give some troubleshooting suggestions

Best Regards,

Amy Luo