Hello,

I would like you to confirm output behavior when we use interleave mode.

The data condition is when we input digital data for DAC A and DAC B one by one.

* According to datasheet, there is following section which explain behavior of interleave mode.

7.3.3 Single-Bus Interleaved Data Interface and Timing

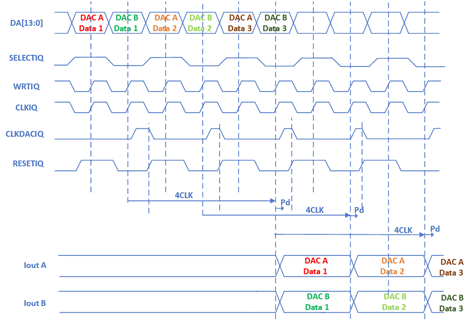

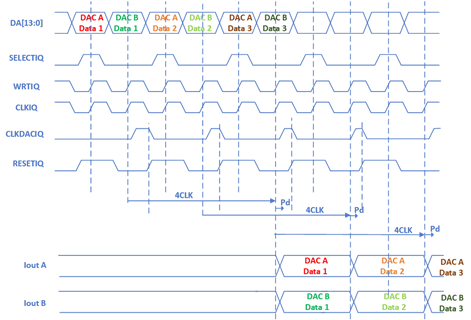

For this section, I understand as shown figure for above sentence.

1. When RESETIQ become high, DACCLKIQ from output of divider(div /2) become low. However, maintain "DAC A Data 1" by rising edge of WRTIQ.

2. When RESETIQ become low, DACCLKIQ will rise up accompanying the rise of CLKIQ. After 4CLK(tlat) later + Pd, DAC A Data 1 and DAC B Data 1 will be output for each output port.

Same thing will continue for DAC data 2 and 3.

Then I have following questions.

Q1. Af first, is my above understanding and figure correct ?

Q2. If Q1 is correct, is my understanding when user try to pair DAC output A and DAC output B, data rate should be CLKIQ / 2 even in the fastest case correct ?

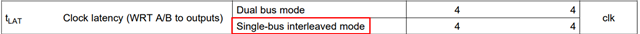

Q3. If Q1 is correct, I think that explanaion of "tlat" is strange.

Because, in case of interleave mode, when RESETIQ is high, DAC does NOT latch input data. CLK which latch for DAC is CLKIQ (In fact, CLKDACIQ)

Therefore I think that "WRT A/B" should be "CLKIQ or CLKDACIQ" in case of interleave mode. Could you please confirm about this and give me your feedback ?

BR,