Hi

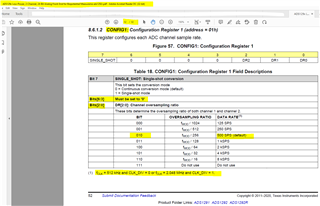

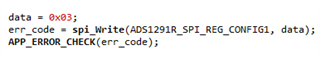

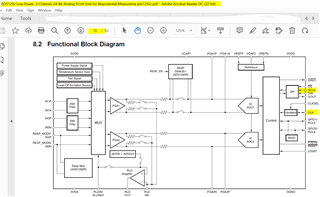

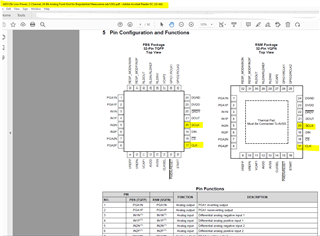

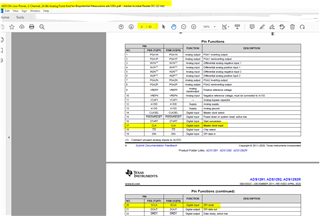

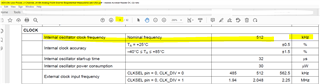

I'm measuring wrist ECG with ADS1291.

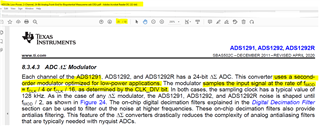

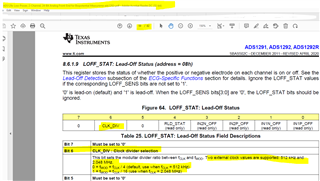

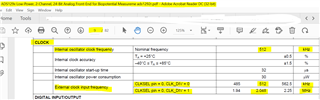

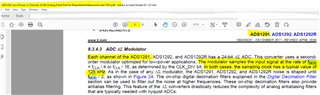

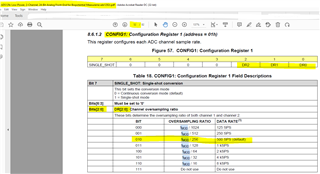

Currently, I set it to 500 sps and collect data.

I'm measuring it in 30 seconds, but I got 41,000 data.

I think it's sps = hz.

So I think we should get 15,000 data if we measure 500 sps and 30 seconds.

I wonder if I'm wrong.

Help me. Thank you..