Other Parts Discussed in Thread: AFE58JD32LP

Dear TI support team,

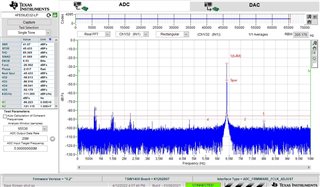

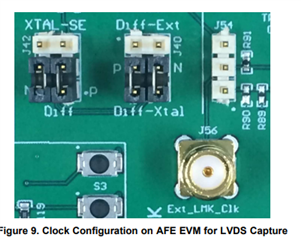

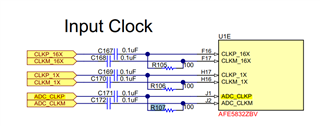

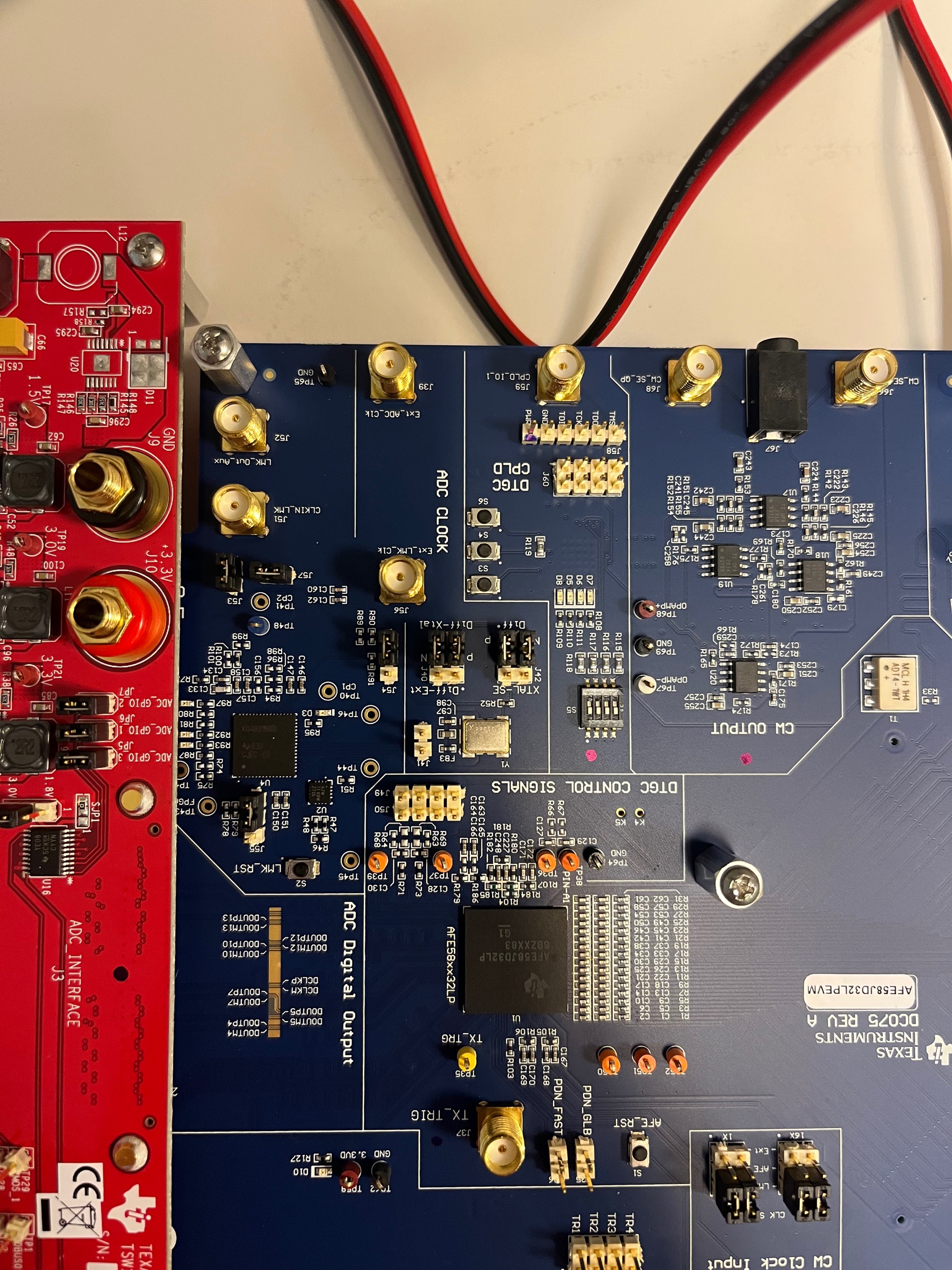

I'm setting up a system with the AFE58JD32LPEVM and TSW1400EVM following the procedure described in the user's guide SBAU326–August 2018 of the AFE58JD32LPEVM. The setup is the same described in figure 4 of the guide except for the optional external clock reference that i did not connect. I've followed the instruction for "LVDS Capture only" but instead of getting a sharp peak at 5 MHz as shown in Figure 17 at page 12, I'm getting a peak at 6.4 MHz. I attach the screenshot from the HSDC Pro showing the mentioned peak at 6.4 MHz, but if i connect my generator to a spectrum spectrum analyzer i see the peak as expected at 5 MHz. Can you help me in setting properly the system to observe the peak at 5 MHz in HSDC Pro as expected from Figure 17?

Thank you very much,

Marco Travagliati