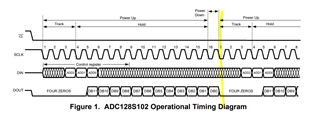

In figure 1 waveform it shows there should be 16 clock cycles for reading Dout. What happens if there are 17 cycles before we pull the CS high?

Is it alright to use a pull-up resistor on Dout?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

In figure 1 waveform it shows there should be 16 clock cycles for reading Dout. What happens if there are 17 cycles before we pull the CS high?

Is it alright to use a pull-up resistor on Dout?

Hi Joey,

I'm actually not sure what happens with more than 16 clocks and we'd need to try to test this out. Has the customer already tested this configuration out and if so, could they share their results? One of the following would happen:

1.) "0" is clocked out for extra clocks (most likely)

2.) the shift buffer wraps around and we begin clocking out the MSB again on the 17th clock

3.) the LSB value is shifted out again (least likely)

There are no issues with pull-ups on DOUT provided the value is not so low that it draws enough current to mess with the VOL/VOH levels. It will cause increases in power-draw for the system as the DOUT line toggles.

Hello,

To add some clarity to the first part of the question.

As you reference, figure 1 shows what happens when more clocks are provided within the same CS frame.

In this particular case, if only one extra clock is provided, 17 total, then the device will behave as the first clock in the second conversion cycle, highlighted in yellow below.

The DOUT pin will output zero, and the device will enter track mode of a new conversion cycle. Once CS is brought up, these operations will cease.

Regards

Cynthia