Hi Experts,

Good day. We have this query from Cx (he is using free email):

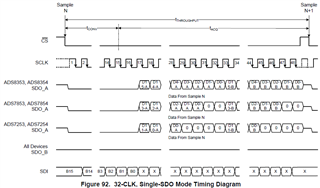

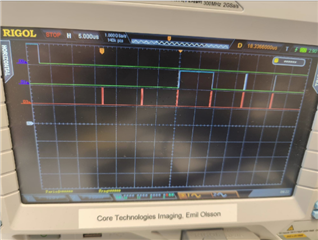

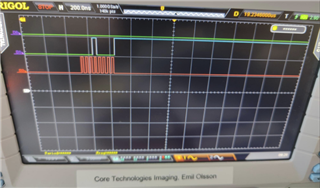

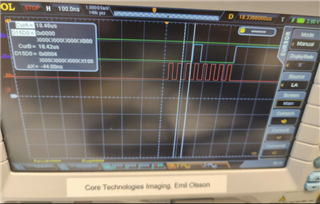

ADS7853: 14 Bits, 1 MSPS, but I am only receiving a 1kbps sampling rate when reading via SPI, do you have any advice on what could be the bottleneck? Do I need to use DMA to go faster than that?

Thank you.

Regards,

Archie A.