Other Parts Discussed in Thread: LMK04828

Hello Colleagues,

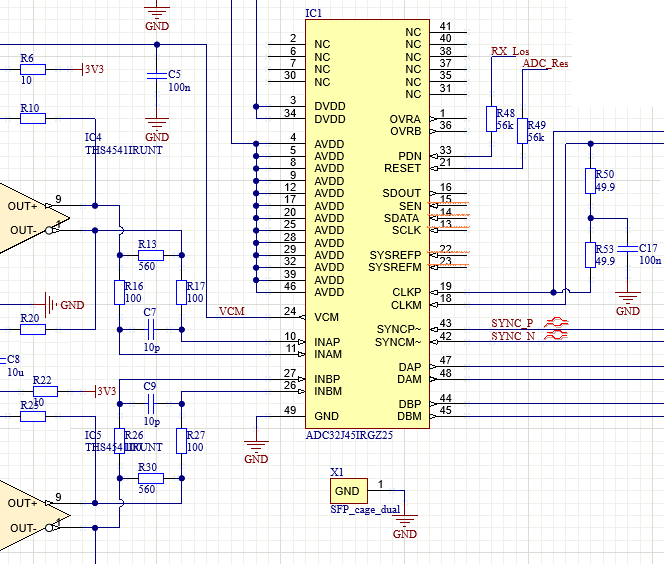

I choose the ADC32J45 for developing a measuring device in a kicker system of the XFEL (European Free-Electron X-Ray linear accelerator).

The first results show a strange noise, which seems to be dependent of the signal value. I posted a plot of the VIVADO Logic analyser, witch shows the received signal (rxdata[15:0], where the two LSBs are always zero). The conversion speed is 160MS/s, SYNC was successful, JESD data came without any errors, so the problem must be at the analog side.

The Noise peak-to-peak level is approximately 1% of the ADC range, what is not acceptable for a 14bit ADC.

At the analog input side, a THS4541IRUNT fully differential OpAmp was used, as recommended in the Eval-Schematics.

My questions: Does anybody know, what kind of noise is that (e.g. sampling-glitches) and what is the reason for it?

Could the reason be a damaged ADC?

Is there any solution, e.g. extra filtering at the ADC input pins what can prevent that kind of glitch?

Thanks in advance for answers!

Regards

Artur Boebel