Hi,

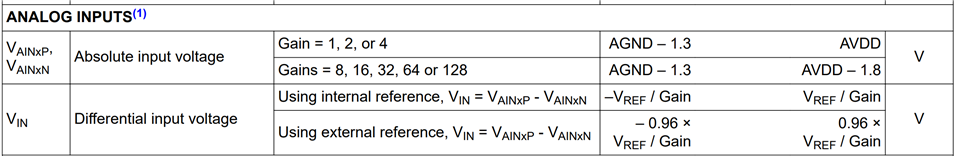

I am using an external reference, and according to the datasheet (Page 7) the VREF is multiplied by 0.96.

Is there any information on how consistent that (0.96) is across different chips and temperature range. Or is it something that I should calibrate for each unit.

Thanks and regards.