Part Number: ADS131M06

I appear to be having a problem setting up an ADS131M06. I can read back the registers I set but there appears to be no difference in the output.

I've checked the signal with an oscilloscope to check the edge quality and with a logic analyzer to ensure longer bitstreams are correct. In addition the fact that the readback of the register gives me the same value as the one I wrote it suggests that the writes are performing correctly which provides a secondary check of the signal timing and bit order.

I write a value of 0x3F1E to the CLOCK register which should result in

channels 0-5 enabled

OSR bits set to 7 for an OSR of 16256 and a conversion rate of 250 SPS given my clkin rate of 8.192MHz

PWR bits set to 2 or default high resolution

In addition I write a value of 0x511 to the MODE register which should result in

register and input CRCs disables

reset bit left high

SPI timeout enabled

Most lagging channel controlling *DRDY

*DRDY driven high when no data ready

*DRDY an active low pulse of 4 clkin or ~0.5uS at 8.192MHz clk rate.

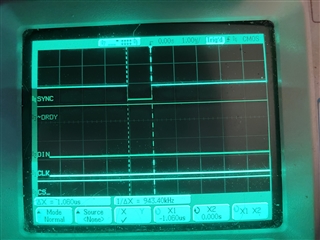

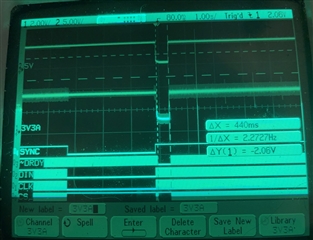

However, I'm seeing a *DRDY rate of 4kHz+ with the signal being mostly low as shown

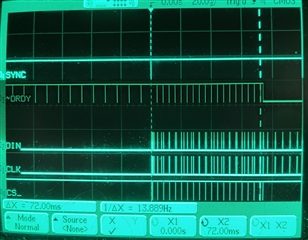

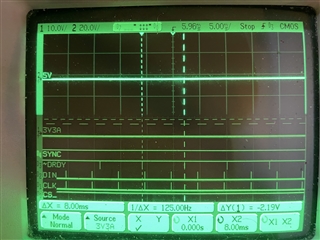

The next shot shows the write sequence for the CLOCK register

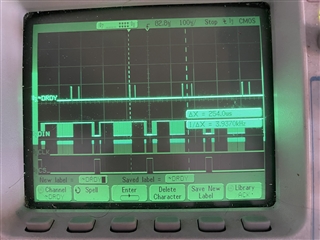

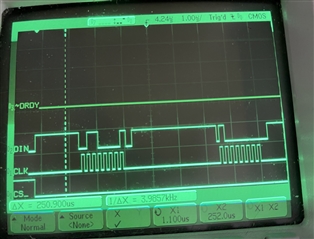

And two images showing the details of that write

first the command

And then the register value

I have the same sequence for the writing of the mode register. I don't think it adds much information though.

I'm sure I'm either missing or misunderstanding something in the datasheet but at this point I don't know what it is. I'd have expected to get a narrow low pulse from the *DRDY line at ~250 - 500Hz given those settings (up to 500 because of internal buffering) but I'm getting a majority low line and at 4kHz. The settings don't seem to affect the behaviour. Any ideas as to what I'm missing?

Robert