Hi Abhishek,

As you told it was capture issue we could solve it, thank you for your pointers.

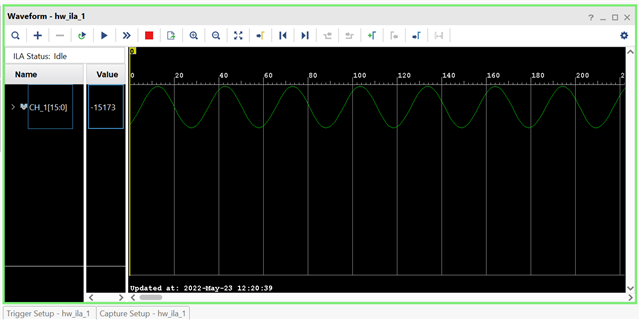

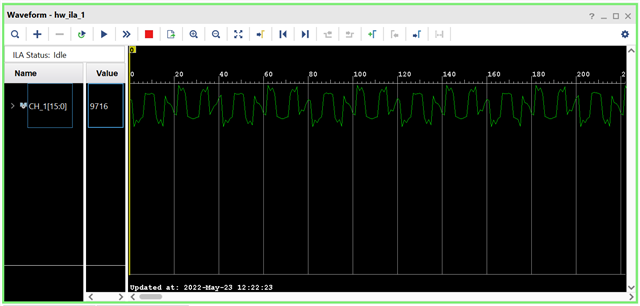

Now, we're facing some more hiccups we're able to see sine wave in ila till 30 MHz sampling clock frequency from 40 MHz output is not coming properly, after this observation we tried to check the same by generating ramp test pattern using spi registers (0x25,0x0040) even the ramp signal was not coming good from 40 MHz we've to do our system till 100 MHz, Your suggestions on this will be really help full.

i'm attaching the snips of ila outputs too for your reference.

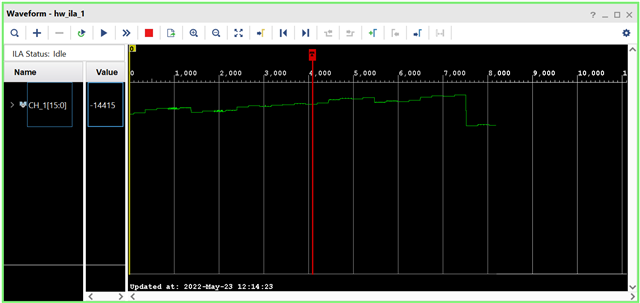

ramp for 30 MHz sampling frequency

ramp for 40 MHz sampling frequency

1 MHz input analog signal 30 MHz sampling frequency

1 MHz input analog signal 40 MHz sampling frequency

we have used Xilinx IDDR to capture the samples