Hi team,

A question from one of our customers:

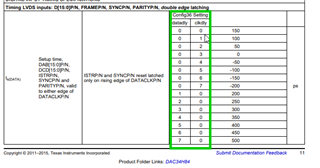

Both the customer supplied DACCLK and DATACLK are 100M, with clock rising edge acquisition A channel giving a value of 0, with clock falling edge acquisition B channel giving a sine wave produced by DDS.

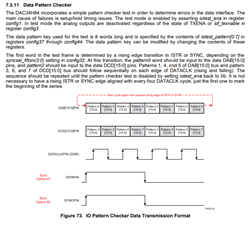

Register Configuration :

addr value

02 0x7082,

00 0xF09C,

01 0x140E,

18 0x2000,

1E 0x8888,

1F 0x1142,

which is 2s-complement, Interpolation factor is 1.

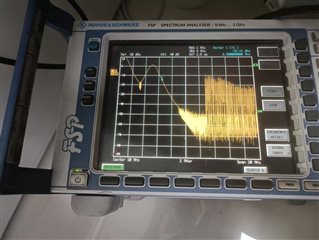

The A channel output is 0, and the B-channel output:

Verified that the registers were read and written correctly. But as shown in the picture , it can output the sine wave that produces 5M frequency points, but it's a little bit more noise, and what's the problem? The customer guesses there is a phase problem with the DAC_CLK, causing unstable waveforms to be generated. Could you make some troubleshooting suggestions

Best Regards,

Amy Luo