Hi,

We're using 6 ADS1220 in one of our product. They are all configured identically in continous conversion mode, communicate through the same SPI bus, and are clocked by the same 3MHz signal (CLK pin). The "start" command is sent through SPI with all 6 CS pins activated, then a single DRDY pin is polled to trigger data gathering of all 6 ADCs from an STM32.

We usually don't have any issue, but some samples answer 0xFFFFFF continuously for a period of time.

When this happens, most ADCs work fine, but one (rarely more) only answers 0xFFFFFF when the continous data is read, and also 0xFFFFFF when the configuration registers are read. This situation may continue for a long time, or disappear after a power-off. It may reappear on the same ADC, or another one. Some systems are often faulty, on others it occured once, for most of them never (I don't have a very precise estimate, but I would say <10 samples for 200+ products).

We managed to measure the SPI signal in real time, the MISO line is effectivelly driven high for the time of the CS activation.

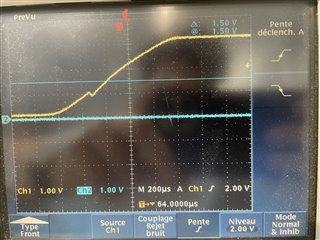

We found an implementation error on our side : The external 3MHz clock had a duty cycle of 25% instead of the 40-60%, but since we lack a reliably faulty device we cannot easily confirm this cause.

Could this error explain our problem? Or could this problem be related to a known issue or common misuse?

Is there an errata for this chip?

I know this description isn't complete but explaining the complete system and investigation would be quite lengthy ; Please feel free to ask me for more details if required.

Thanks,

Etienne.