Other Parts Discussed in Thread: , CDCE62002, CDCM6208, SN65LVDS101, CDCLVP111-SP, LMX2615-SP, LMK04832-SP, SN65CML100, CDCLVP111, CDCE6214

Hi,

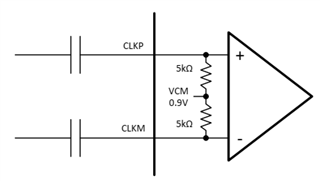

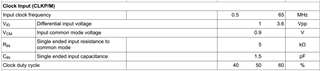

The ADC3683 datasheet specifies no minimum VID. Is there one? Will this work if driven from a standard LVDS driver (AC-coupled)?

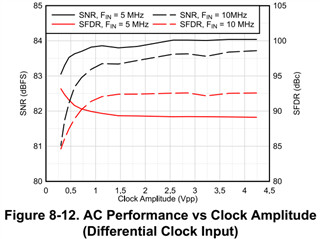

Figure 8-12 makes it clear the higher the driving VOD, the better the performances.

Driving CLKP/M from a LVDS driver (eg FPGA IO) is not a good choice since typical LVDS VOD is 350mV (so, far left on the above graph).

What type of driver would you recommend to drive CLKP/M differentially and get a VID of > 1.5V? Can you provide a reference design?

Thanks!