- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Support team,

My customer inquires total delay time from SPI command received to output set, could you support?

*What is internal delay time from SPI command received to output start changes?

*What is settling time from output start changing to output target value?

Thanks,

Koji Ikeda

Hi Ikeda-san,

The delay should be very minimal, <300ns. There is a very short digital delay, maybe <50ns, and then a period where the track-and-hold glitch reduction circuit is engaged. During that period the R-2R ladder is changing voltage but the output is static. After that period, the output will start slewing. If the output is at 0V, there is a period where the output amplifier is in overdrive recovery. That period can be 1-2µs. If the output is >2mV, usually there is no overdrive recovery delay.

Thanks,

Paul

Paul-san,

Thank you for your support. Settling time information is not clear for me, so could you explain more?

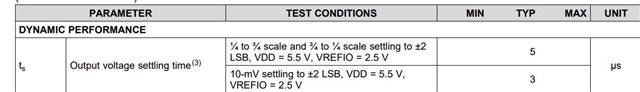

Does 5usec setting time mean the time for 1/2 of full scale step from start output changing?

Does 3usec settling time mean the time of 10mV output step from start output changing?

And if output is 0, another 1-2usec is needed for recovery delay, is my understanding correct?

Thanks,

Koji Ikeda

Hi Ikeda-san,

The 5µs and 3µs specifications include all delays from the final latched edge of the SPI/I2C command and the output settling.

When the output starts at 0V, there could be an additional 1-2µs delay.

Thanks,

Paul

Hello Paul-san,

They ask another question. What does "sequential DAC update wait time t_DACWAIT min 1usec" mean?

Thanks,

Koji Ikeda

Hi Ikeda-san,

This would be minimum time you need to wait between LDAC commands for the same channel. This means that the max update rate supported by the architecture (regardless of settling time) would be 1MSPS.

Thanks,

Paul