Other Parts Discussed in Thread: TEST2,

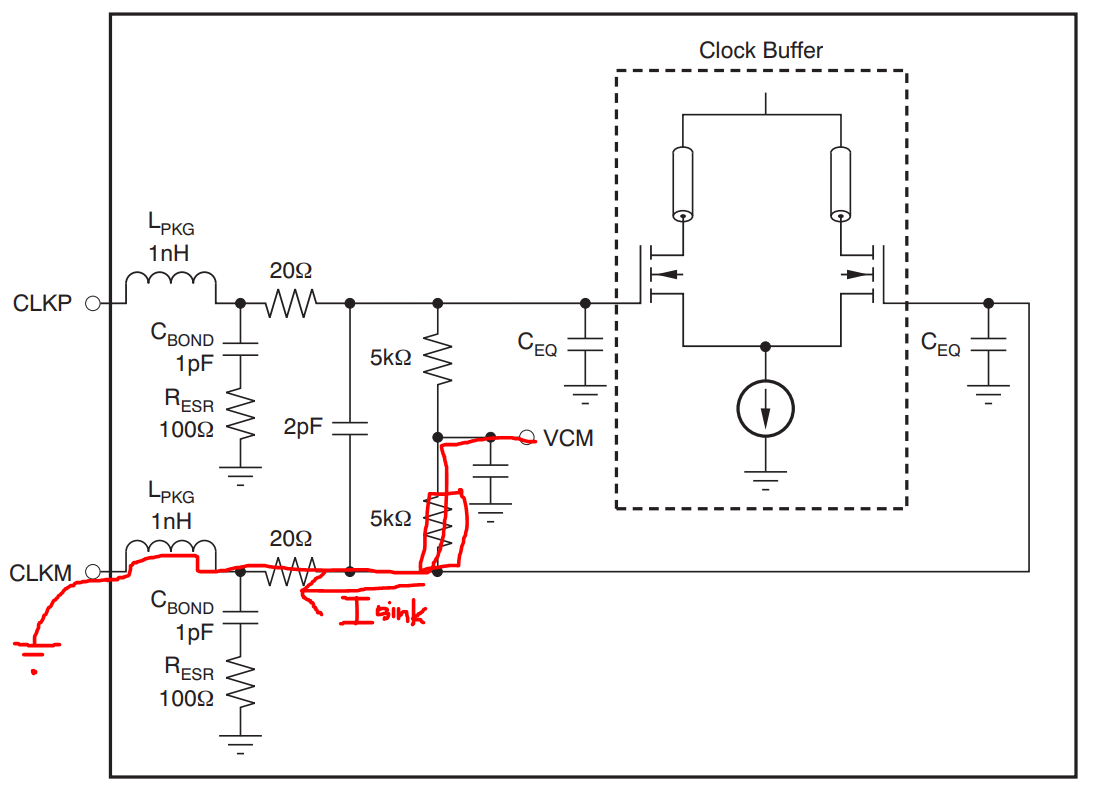

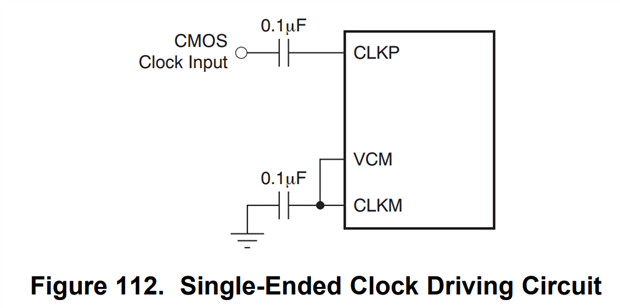

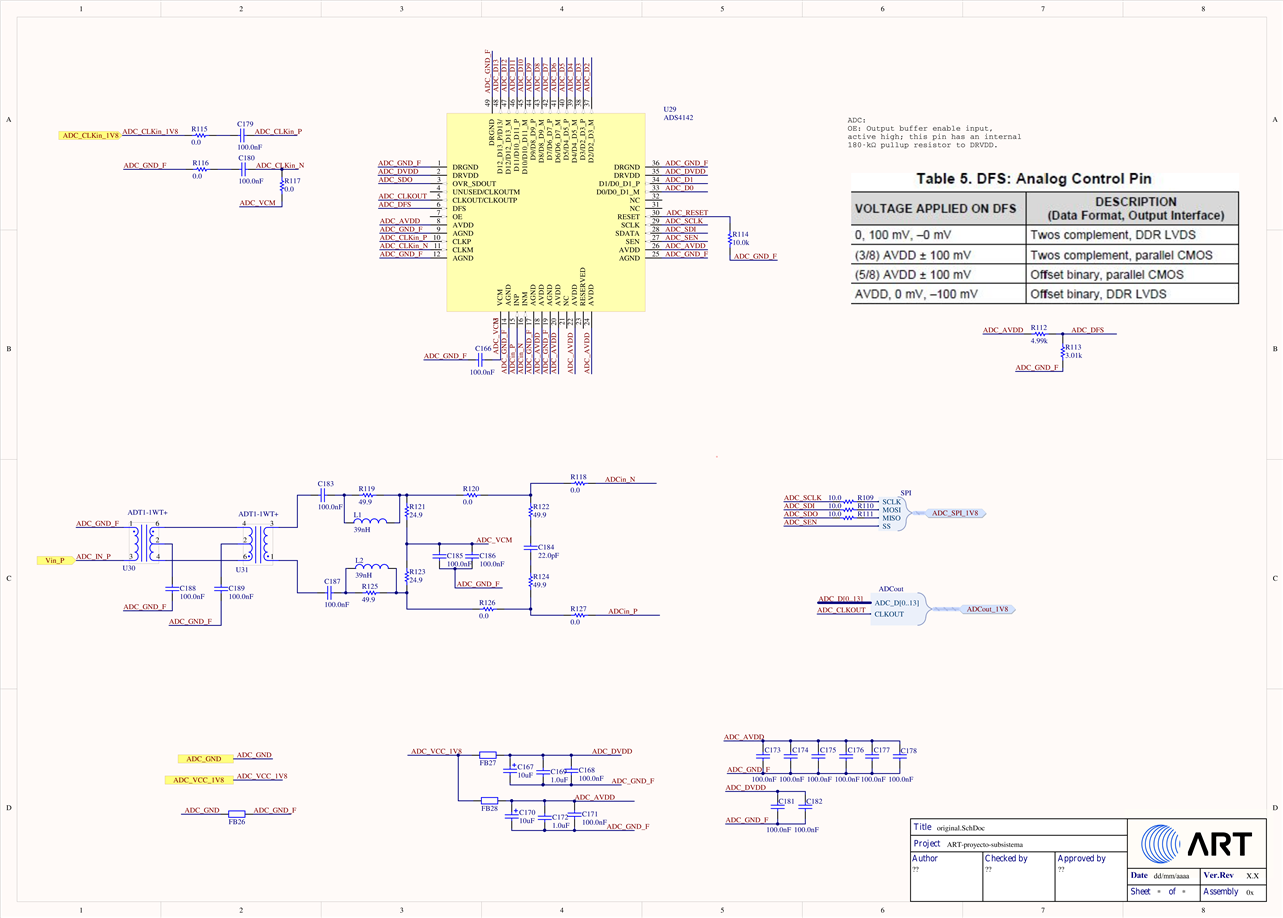

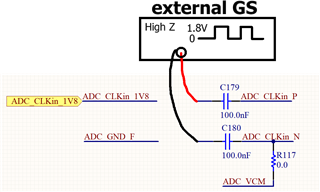

Hi, I'm trying to understand the circuit around Clk input. I see it allows for differential signals between CLKN and CLKP, and the circuit for a differential sinewave clock simply inputs into these pins. However, the CMOS example, instead of connecting CLKN to GND as I would expect, is connecting this pin back to the Vocm signal.

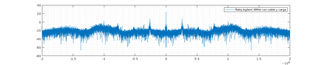

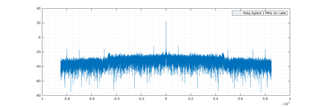

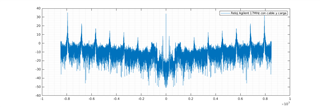

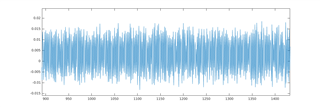

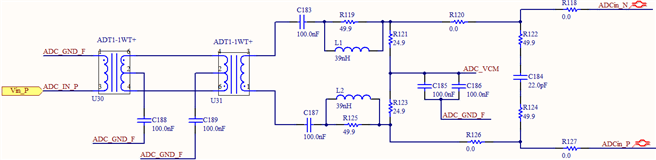

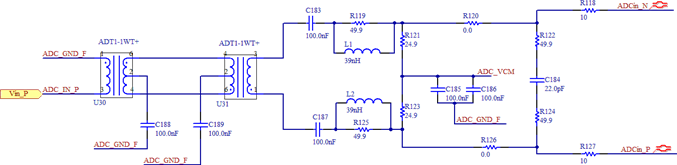

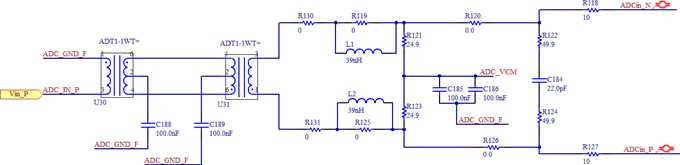

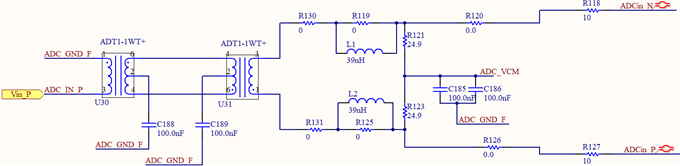

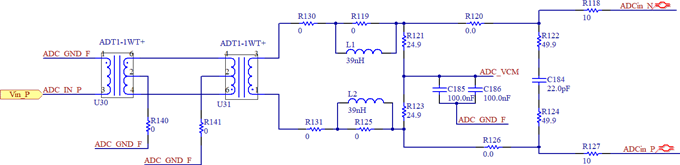

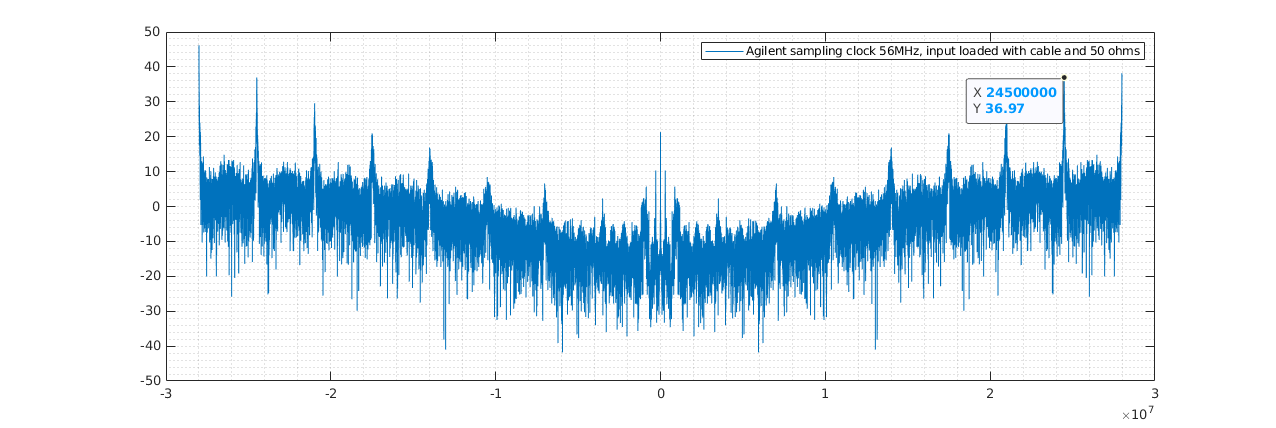

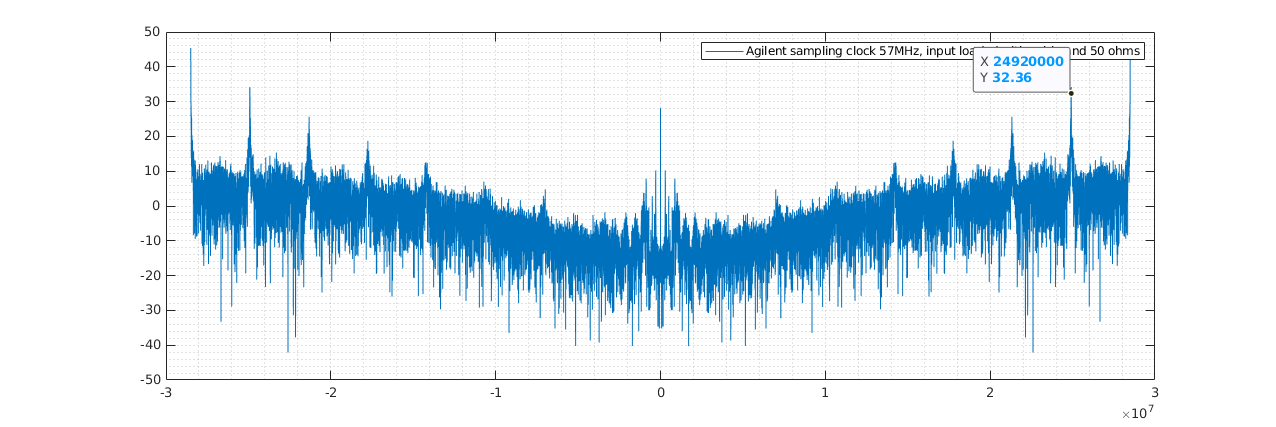

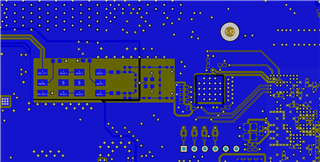

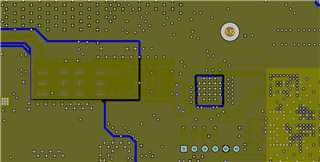

I have implemented my own board using this as a reference, as well as the input circuit based on two transformers. Measuring with an oscilloscope, I am seeing a very high noise appearing at Vin_p and Vin_n, and it looks like clock phase noise is being transferred to the input via Vocm signal.

I am not entirely sure if my noise is coming from the clock, but still I don't fully understand the clock input circuit, so I would like some insight on this. Could I just connect my 1.8V cmos clock to CLKP and CLKN directly to GND?