Other Parts Discussed in Thread: CDCE62005,

I am doing a project using DAC 3283 using artix 7 FPGA and also using CDCE62005 the requird data clock and dac clock is generated and gave input to DAC3283.

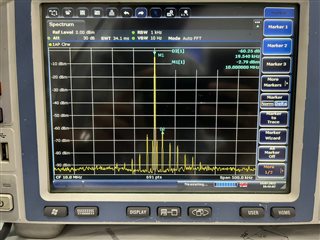

DAC_CLK Sampling frequency is 400 msps . The digital input given to DAC3283 is 10MHz using DDS complier in xilinx vivado 18.2 tool. The analog output we got was

10 MHZ with 3.22 dbm which is observed by using spectrum analyser. but ckecking the spurious level by setting 1Kz restive bandwidth(RSW) and vedio bandwisth(VBW) around 10 hz with span range of

500KHZ , we got 57 dbc . In data sheet , showen that for 10mhz spurious level will be around 80dbc to 85dbc. Now for my generated 10Mhz needed spurious level which is greater than 75.

and how can i achieve it ?K

inldy reply with better solution.

Thanks in advance