Hello,

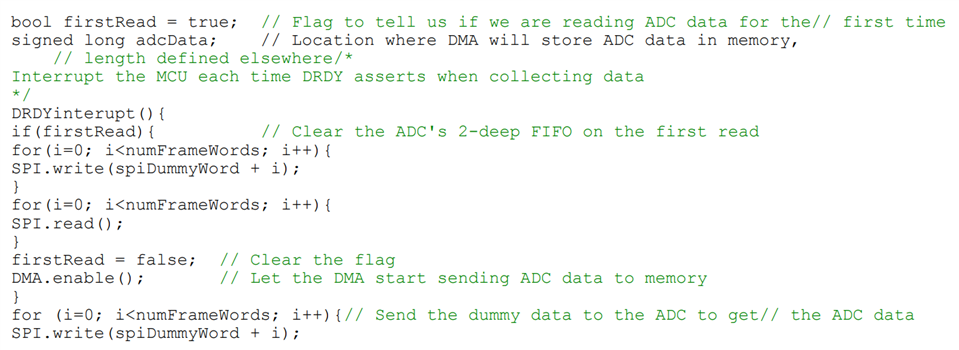

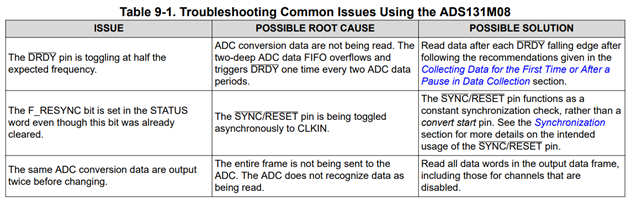

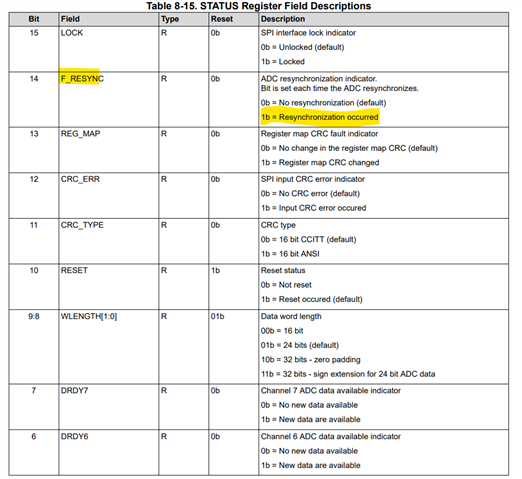

I have a technical question about the use of the ADC chip ADS131M08. I am using the SYNC input pin to start the conversion but then I have to perform 2 dummy reads before the data is available from the FIFO, I have read that this is not really the right way to use the SYNC pin, its not intended to be used as "Start Conversion" is that correct? Also is there a way of disabling the FIFO, so that once DRDY pin output goes low, then I can read the data available immediately? I am operating in Continuous Mode.

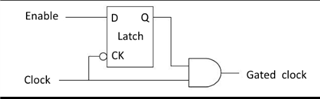

Just to add, although I'm using this in continuous mode, I do pulse the SYNC input low to synchronize for every sample I need, then I wait for DRDY to go low then I read the data. The reason I do this is because I need to adjust the rate slightly of my sample period and i intended to do this by the SYNC pulse. Perhaps its better for me to do this adjustment by varying the CLK input frequency slightly and not pulsing the SYNC input every sample. (I've set the OSR to 128 and my crystal is 8MHz).

Kind Regards,

Phil Spanton