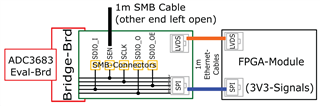

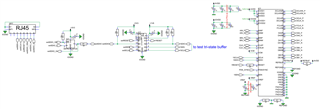

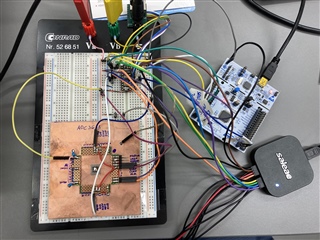

In our development application we need to interface the SPI of the ADC with our FPGA and therefore unsoldered R139, R140, R141, R142 and R144. Then we populated R133, R134, R135, R136 and R137 with 0R resistors to route the SPI lines to the FPGA connector. The adapter PCB from J15 to the samtec high speed connector is plugged in and we manufactured our own breakout board from the samtec connector to SMB and one RJ45 connectors. We use the SMB connectors to interface to our FPGA and the RJ45 connector which is in parallel was left open.

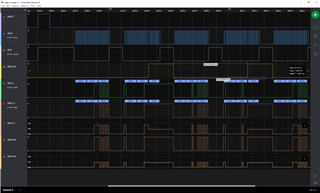

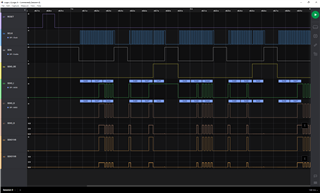

No SPI communication was possible. When probing arround with a scope we noticed that SDIO_O is stuck at the last state of SDIO_I after SDIO_OE switched the bus driver IC to high-z and the adc is not able to drive SDIO_O through the level shifter IC.

When connecting a normal ethernet cable to the RJ45 connector and leaving the other end open, suddenly SPI works flawlessly. When the SPI signals are instered into the other end of the RJ45 cable and the SMB connectors are left open, the same problem occurs as without the dead end ethernet cable.

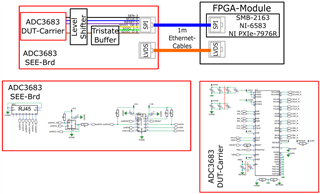

We also experience the same problem when using the ADC on our own development PCB where the SPI signals are routed through the same level shifter and tristate buffer as on the eval board and then routed to an RJ45 connector. Here adding dead end cables or capacitors in the pF range to the SPI wires does not solve the problem.

Any tipps on how to overcome this challenge are welcome!