Hello.

I'm going to use ADS7138, and I have 2 questions about it, just to be clear.

(1) Is it ok if DVDD = 3.3V and AVDD = 4.096V? That is, can AVDD be greater than DVDD?

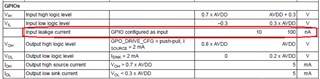

(2) Please check picture below, its from page 8/90 of datasheet. I will use all 8 inputs as analog inputs. The question is, when the pin is used as analog input, the maximum input leakage is also 100nA?

Regards,

Jeferson.