Hi,

we observe a weird behaviour.

We switch the ADC settings at every conversion:

state 1: GAIN = 128, channel 1

state 2: GAIN = 1, channel 2

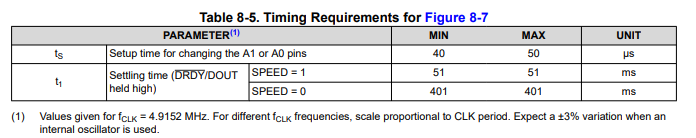

the speed is always high (80 Hz).

If everything is OK, in this test channel 1 (connected to a load cell) reads about 527000; channel 2 reads about 234000 (a potentiometer)

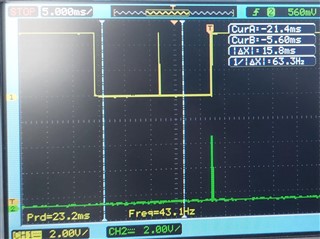

Sometimes we get an out-of-scale reading (for example all 0's or all 1's or also too many 1's :)); see the following oscilloscope tracks (DOUT is yellow, SCLK is green). There is always only one spike at a time (they don't go in clusters) and that happens about 10 times per hour. It happens on both channels.

The problem is there also if we don't change settings (they stay the same all the time and we read only channel1).

Sometimes it also looks like the ADC starts sending data before the clock starts:

We realized that there was a problem: sometimes we started reading the ADC with a delay after DOUT went low:

and it looks like the ADC has a spike, even if not clocked.

Better reading the datasheet we found out that the data must be read within t7 = 12.5ms (figure 8-9), and we didn't find a different value for t7 if you read more than one channel, even if in this case the conversion time raises to 50 ms.

So we modified the firmware to read the data within 12.5ms.

After this modification, the problem is fixed if we don't change settings, but if we change settings at each conversion it is still there, even if with much reduced frequency.

Do you have any knowledge or suggestion about this problem?

Kind regards,