Other Parts Discussed in Thread: ADS42JB49

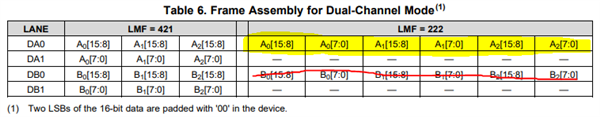

I am reading in my ILA sequence transmission that the M configuration bit is outputting 1, which, based on Table 9, means that there are 2 converters in operation. How do I set M=1 converter? I assumed that was set by changing if Channel A/B was powered down. I have powered down Channel B so I assume the ADC would correctly indicate in ILA that there is only one converter.

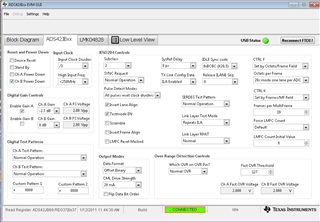

My desired setting of LMFS is 1121. I see that all the other configuration parameters are being transmitted correctly in ILA (with the exception of L which is configured for 2 lanes because M=1 instead of 0). I have attached my settings file below.

Though 1121 is not a listed configuration in the datasheet, it is valid based on this discussion: e2e.ti.com/.../4073194