Hello,

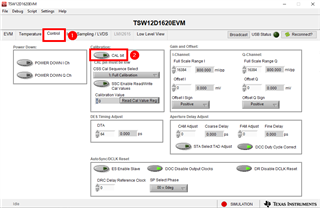

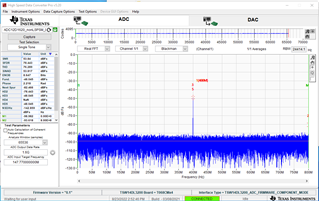

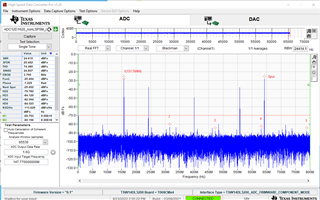

I am evaluating two TSW12D1620 eval boards. I am a seeing a fixed -50dBm spur at 400MHz on both cards with or with a the 1.6GHz clock inputted which make me feel it is something I have wrong in my setup. I am following the evaluation guide and the only deviations from the instructions I had were on step 2.13 where it mentions specific files to select. I found files in the folders that had similar wording but slightly different and I am not sure if those are the issues. Because of the fixed spur I see at 400MHz what happens is I see my 147.77MHz carrier beats with the spur so in my spectrum I see the carrier and a bunch of products of the spur +/- N carrier. I am using an external clock in all cases.

Where can I find the following files just to ensure I am following all the instructions exactly how the guide describes?

Step 2.13

TSW14DL3200_FIRMWARE_COMPONENT_MODE_800M.bin (I only found a file call "TSW14DL3200_FIRMWARE_COMPONENT_MODE" in the folder

ADC12D1620_NonLSPSM_Demux_nonDES_DCLK90_DDR (I could not find this specific file but a version of that typ of file that does not mention the DCLK90 in the name)

Thanks,

Mickel