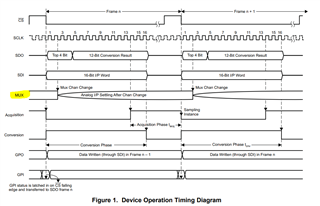

Tq is said to be

Minimum quiet sampling time needed from bus Tri-state to start of next conversion.

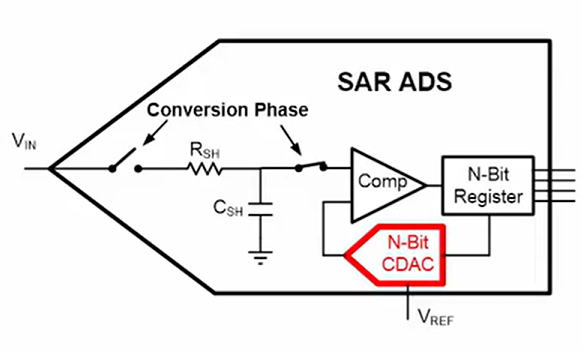

1. How is it different from acquisition time?

2. Why acquisition time and conversion time could be overlapped?

For SAR ADC, there is a sampling capacitor, during acquisition time, the cap should be connected to input pin, during conversion time, the cap should be unconnected to input pin, then my understanding is that the acquisition and conversion time could not be overlapped.

3. The acquisition time start from 14th clock and ends at next instance CS pulled from high to low. What if the duration is lower than 325ns requirement? What data could I get through SPI reading? Wrong data or previous conversion data?