We are in the process of designing an instrument using the ADS8167. We do have a development board on order for testing, but would like some additional information which is not clear from the datasheet.

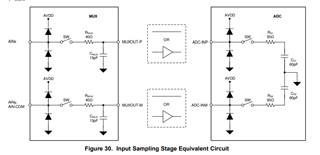

The input channels we are digitizing are AC and have the characteristic of saturating the front end (either + or - rail) during an output phase, and we will be sampling 8 channels as they come out of saturation and settle. The final stages feeding the ADS8167 multiplexer is a rail-to-rail single supply OpAmp, with drive capability of about 50 to 100 mV offsets from the rails. Our desire is to allow the full ADC range to be used on the unsaturated signal out of the final stage. We are considering running with the internal reference and use the REFby2 output to set the center voltage of the final stage. The AIN_CFG would be set for separate channels (0), COM_CFG set to 1 with AIN-COM wired to REFby2 for pseudo-differential operation, and the REFby2_MRG register would be set to provide an offset of ~100 mV (01100001b).

Are there any issues with this approach?

In order to save a regulator we are considering powering the final stage OpAmp from 5V (same as the ADS8167 AVDD) which would allow the ADC to see values close to 1V greater than Vref/2, instead of powering the OpAmp from Vref + 0.2V which would limit the ADC input (ADC-INP - ADC-INM) to Vref/2 + 0.1V (which appears allowable from the datasheet). This leads to the following questions:

- What happens if an input to the mux goes above Vref + 0.1V - is there crosstalk between the mux channels?

- What happens if the ADC attempts to read something above Vref/2 + 0.1V in pseudo-diff mode?

- Are we correct in assuming that the ADC will report inputs between Vref/2 and Vref/2 + 0.1V as 0xFFFF in pseudo-diff mode?

- Are we correct in assuming that the ADC will report inputs (ADC-INP - ADC-INM) between -Vref/2-0.1 and -Vref/2 as 0 in pseudo-diff mode?

Figure 22 in the datasheet shows Noise Performance vs Temp. Am I correct in assuming this is with the internal 4.096V reference? In Figure 24 a graph is shows noise with varying voltage, so I assume it has an external reference. However graph 24 seems to show worse noise at 4.096V when compared to the 25C point on Figure 22. Can you help me understand that?

Thanks, Chip Weller