Other Parts Discussed in Thread: ADS8505, , ADS8509

In an application using the ADS8508IBDWR, there seems to be some disturbances to the output digital codes.

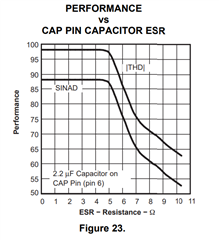

Investigating has shown the issue might be related to the tantalum capacitors selected.

1) Are Tantalum capacitors truly needed - as the DS indicates for CAP, REF, VANA?

2) If they are required, are there any parameters besides capacitance that need to be considered?

Regards,

Darren