Hi ,

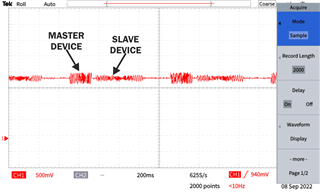

I am implementing HART communication protocol in my two devices let say Master and Slave both are working on 1200 baud rate and odd parity , every time Master sends request query Slave gets each and every packet but when Slave sends response to master it miss some packet or changes some bit for example( i am sending HART in ascii i.e to 0x48 0x41 0x52 0x54 but at master is receiving to 0x48 0xC1 0x52 0x54 ).

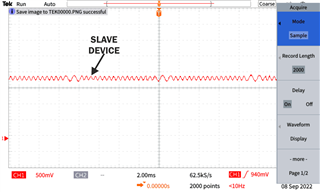

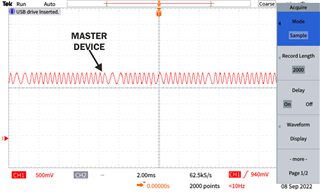

I have checked on digital scope may be the change in waveform ? I have attached photos of scope please check an let me know .

also attached schematic i am refereeing for both device .

Please let me know where i am doing wrong .