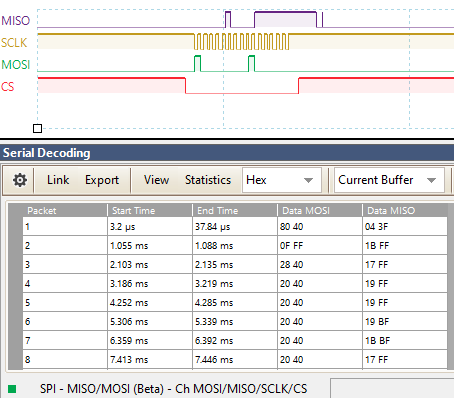

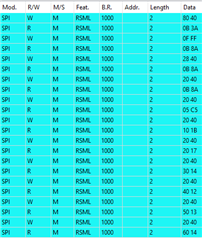

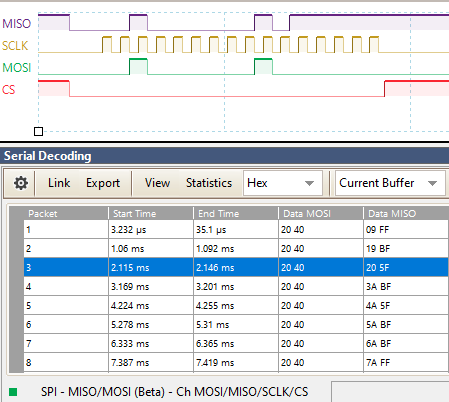

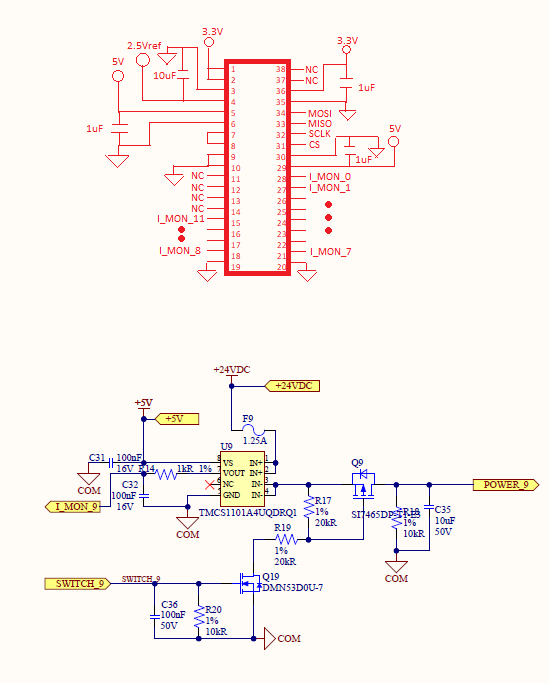

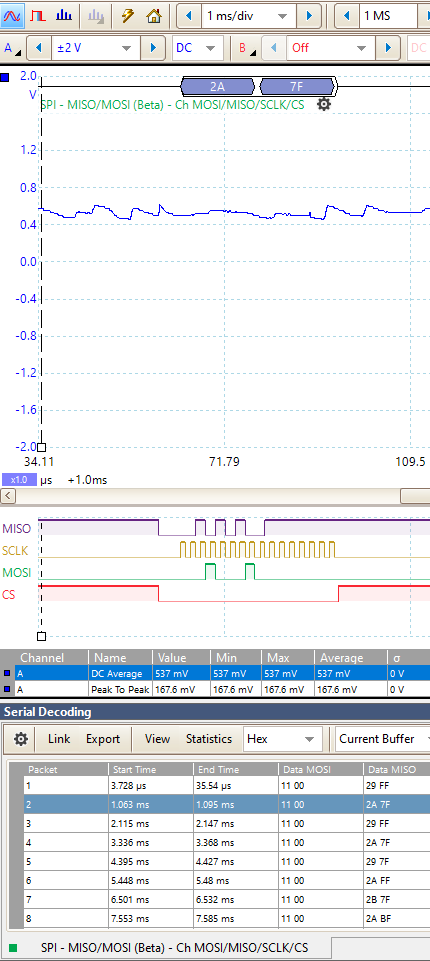

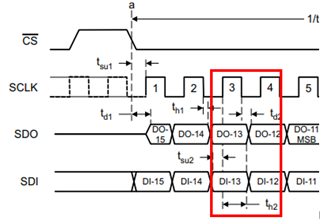

I have an ADS7952 connected to a PIC32MZ using SPI communication (3.3V IO) with all 12 channels connected to current monitor voltage outputs (0-5 V). For referance, the +VA = 5VDC; +VBD = 3.3VDC; Vref = 2.5VDC; MXO is tied to AINP; and we are using range 2 setting (2xVrev). I have tried setting it in manual and auto modes to output the 12 channel values but all the replies from the ADS7952 are 0x1BFF. the first byte is supposed to be an incrementing channel number but it doesn't seem to change. I tried sending manual requests for specific channels but the next frame is still 0x1BFF. Am i missing something that will fix the messages from the ADC?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.