Other Parts Discussed in Thread: LMK04828, , LMX2582

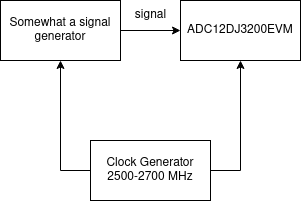

Our system needs to have synced clocks between this ADC and some other part. Ideally, they would share a 2.66 GHz clock for acquisition. I am aware of the possibility to modify the board, but for convenience we want to avoid this. What we are planning to do is feeding this clock signal into CLKIN0 to drive the on-chip clocking (or maybe some lower clock value but synced with the rest of the system). However we don't see a clear solution to this. Following the instructions in page 46, chapter 9.3.5.1 from LMK04828 User Guide Manual, we fed a 1 GHz clock (as a test) into CLKIN0, setting parameter CLin_SEL_MODE to 0 for enabling CLKin0.

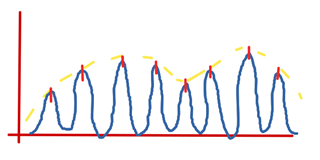

However this doesn't seem to work properly. First of all, we would like to know if we are this way of using the device is possible, or if we are understanding it wrongly. Then, we would appreciate some advice on how to execute our needs. If this information matters somehow, the EVM is connected to a ZYNQ+ ultrascale (zcu102).

Thanks,

Alex