Hello,

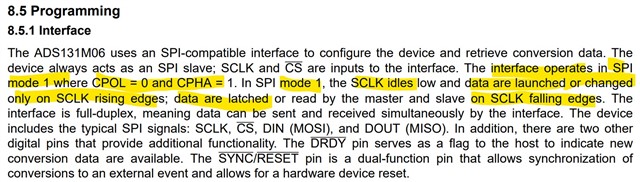

I have problems with ADS131M06. On MCU boot, I am resetting it via SYNC/RESET, then sending WREG to clock register. Here I want these settings:

- External clock source 8.192MHz

- External reference voltage

- All channels

- 250SPS

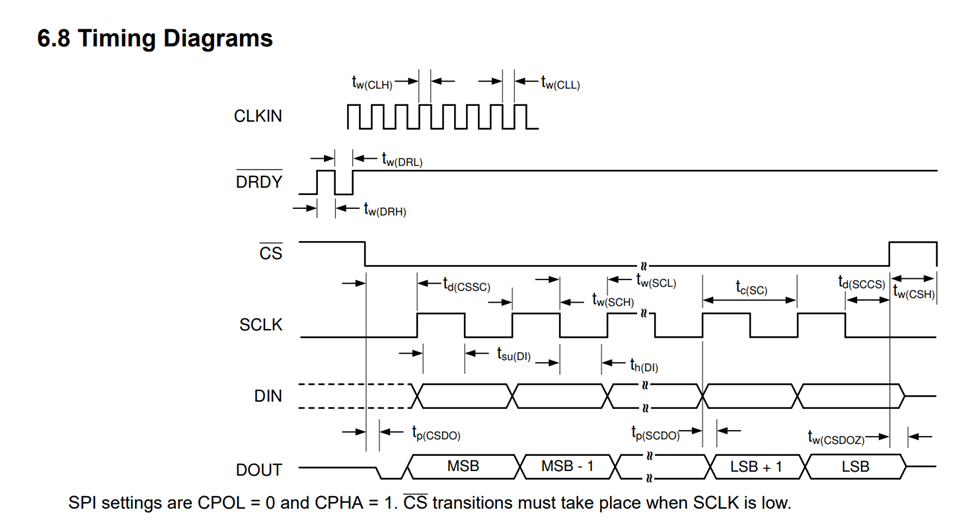

After this sequence, I apply 250Hz signal to SYNC/RESET, and poll DRDY. On falling edge, I am sending NULL command, and reading samples.

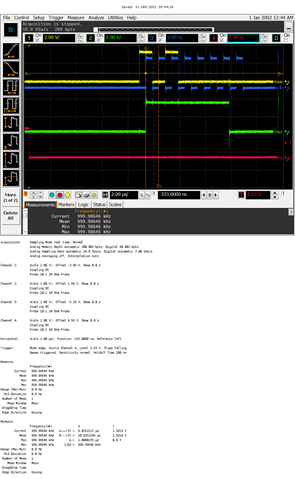

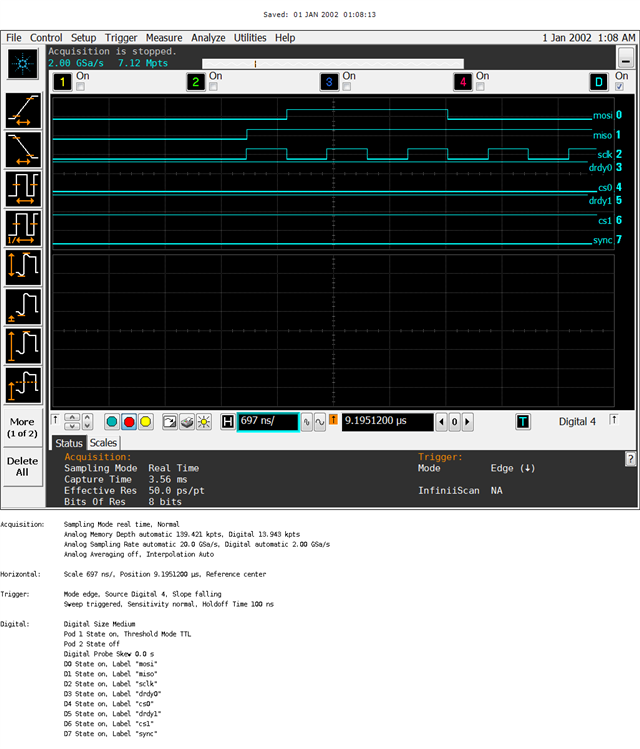

Based on this screenshot, I believe that I am complying with SPI timing requirements. Can you see some mistake?

Here is init sequence:

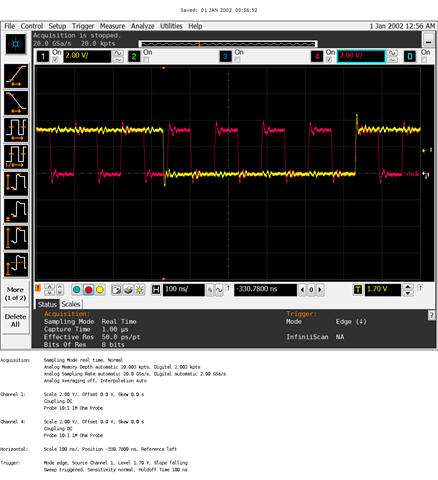

Whatever I am trying to put to clock register, here is what I get on DRDY:

ADC is definitely not operating at 250SPS. Seems to me, that it is operating at 4kSPS, but it does not have enough time to transfer all ADC data in time.

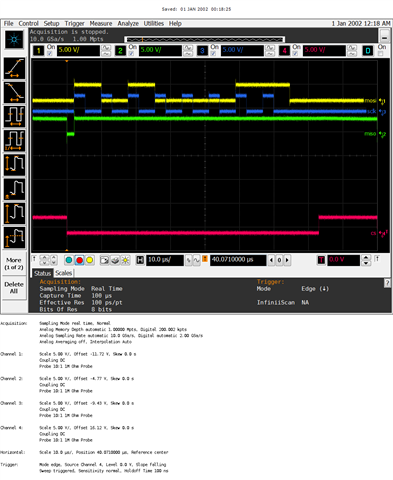

Here are some examples of ADC data transmission:

I do not even know, whether these are actual ADC data, or some mess. I have tied inverting inputs to reference voltage. Right now noninverting inputs are floating, they will be connected to single-ended signal from instrumentation amplifier.

Can someone see what am I doing wrong?

Thanks in advance,

Stanislav