Other Parts Discussed in Thread: CDCE6214, ADC3683

Hello,

In the ADC35XX EVM GUI software for the ADC3683EVM only 2 wire mode is supported by the onboard clock generator IC.

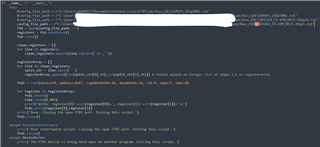

Is there any possibility to use the onboard CDCE6214 for 0p5 wire mode as well e.g. by feeding an external clock signal into the secref input and setting the registers of the CDCE6214 via the ADC35XX EVM GUI SW and the FTDI chip over I2C?

If so, how do I tell the software to set the clock generator IC correctly?

I would like to use the ADC3683 with 0.5-wire LVDS in real decimation mode with a decimation factor of 4, 18 bits and a sampling rate of 65 MSPS.

Is it easier to input the 65 MHz sampling clock and let the CDC multiply it with 4.5 to get the 292.5 MHz DCLKIN or the other way round?

Thank you in advance and best regards,

Lukas

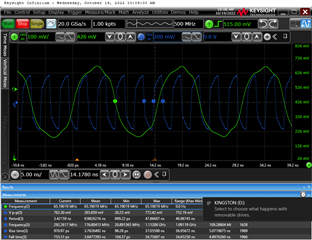

blue: DCLKIN, green: CLK

blue: DCLKIN, green: CLK