Part Number: ADS54J64

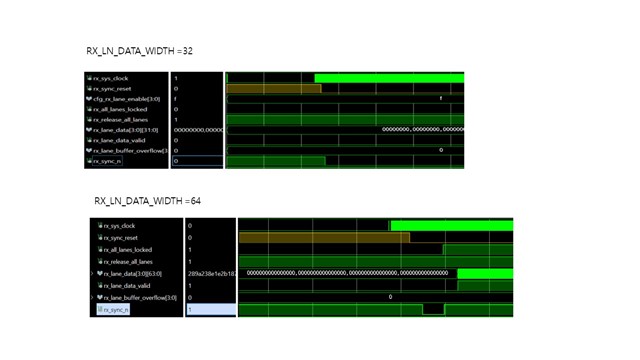

When I set RX_LN_DATA_WIDTH =64, I can successfully receive 64 width user stream of JESD204B IP.

However, when I set RX_LN_DATA_WIDTH =32, I cannot receive 32 width user stream of JESD204B IP.

Which parameters should I change?

<jesd_link_params.vh>

`undef RX_LANE_DATA_WIDTH

`define RX_LANE_DATA_WIDTH 32

<gth_8b10b_rxtx.sv>

if (TX_BYTES_PER_LANE == 4 && RX_BYTES_PER_LANE == 4)