Other Parts Discussed in Thread: ADS54J60

Hi Team,

Use ads54j69 to achieve baseband bandwidth of more than 320M sampling.

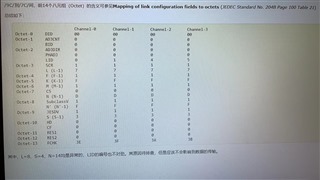

Can the Jesd204b link only be configured for 4222 and 2242 modes? Thanks.

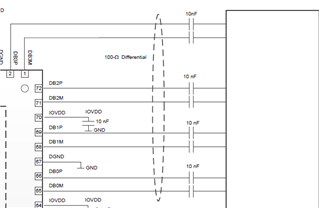

Among the four outputs, can I choose any number of valid outputs?

Best Regards

Charlie Xiao