Other Parts Discussed in Thread: TSW14J57EVM, , DAC38RF82

Hi team,

One of our customers has some questions to ask you. Requesting your kind guidance here.

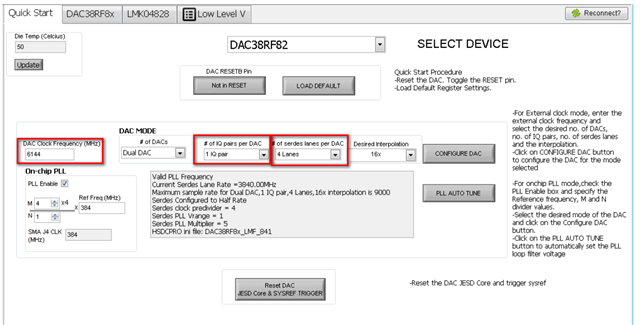

1. When configuring the DAC GUI, in the Quick Start tab, there are " 1 IQ pair " , " 2 IQ pair " , and " real input " in the" # of IQ pairs per DAC" , what do they mean?

2. what is meant " # of serdes lanes per DAC "?

3 . what is the relationship between "DAC Clock Frequency (MHz) " and Sampling rate .

4. LED D8 " JESD sync " does not light on DAC38RF82EVM, how to resolve this, does it mean the DAC38RF82EVM and TSW14J57EVM are not synchronized successfully?

5. when clicking on “Reset DAC JESD Core & SYSREF trigger ”as per the procedure, LED D1 on the TSW14J57EVM goes off and on again, does it mean that the DAC EVM did not successfully establish a simultaneous connection to the TSW EVM?

Best Regards,

Amy Luo